| 題名        | 情報革命の時代を生きて                                                            |

|-----------|------------------------------------------------------------------------|

| Title     | A Personal Journey Through the Information Revolution                  |

| 著者名       | カーヴァー・ミード                                                              |

| Author(s) | Carver Mead                                                            |

| 言語        | 日本語                                                                    |

| 行事名       | 第 37 回(2022)京都賞記念講演                                                    |

| 出版者       | 公益財団法人 稲盛財団                                                            |

| 発行日       | 2024年1月31日                                                             |

| 開始ページ     | 1ページ                                                                   |

| 終了ページ     | 13 ページ                                                                 |

| URL       | https://www.kyotoprize.org/wp-content/uploads/2024/01/2022_mead_jp.pdf |

英語版テキストURL: $\underline{\text{https://www.kyotoprize.org/wp-content/uploads/2024/01/2022\_mead\_en.pdf}}$

# 情報革命の時代を生きて

# 山の中で育った幼少期

ここが私の育った場所です(Fig. 1)。父はこの発電所で働いていました。私たちはそのそばにある発電所で働く人たちが住む住宅群のこの小さな家に住んでいました。そして、私はこの丘の上にある学校に通っていました。

私が育った頃の発電所(Fig. 2)はそれ自体がハイテクでした。これらのすごく大きな水力発電機は、印象的なものでした。この上には制御室があり、そうした大きな機械類を監視するためにびっくりするような計器類がたくさんありました。

これが通っていた学校です(Fig. 3)。教室は一つだけで、女性の先生が一人でした。彼女はここで1年生から8年生までの全ての生徒を教えていました。学校に行くことは素晴らしいことでした。私は先生の隣に写っています。この学校を8年生で卒業した後、私は町に移って高校に進学しました。

Fig. 2

Fig. 3

## カリフォルニア工科大学での学生時代

私がカリフォルニア工科大学に入学したのは1952年で、当時の大学はこのような感じでした(Fig. 4)。私はそこで普通の学士課程の講義を受講しました。講義の中には桁外れに素晴らしいものもありました。大学ではそれまで存在さえ知らなかったことを学びました。また、いくつかの科目は必須であったため、難しくて大変でした。

私が3年生のとき、チャーリー・ウィルツの教える講義を受講したのですが、それは電子工学に関する素晴らしい講義でした。私たちが学んだ内容の一つは機械システムの電気的模擬装置をどう作るかについてでした(Fig. 5)。この装置で学びましたが、これは当時としては世界最大のアナログコンピュータだったと思います。もちろん、小規模なプロジェクトに取り組むときは、インダクタやコンデンサやオペアンプなどそこにあったもののごく一部を使用しました。そこで学んでいたことがとても面白かったので大学院に進学することにしました。

Fig. 5

Fig. 4

# バイボーラトランジスタに関する学位論文

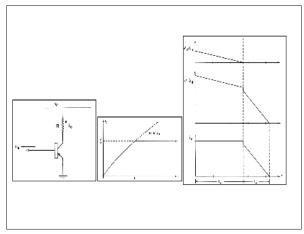

大学院で、当時あったバイポーラトランジスタについて学位論文に向けて研究を行いました。その中でバイポーラトランジスタがデジタルスイッチとしてどのような働きをするのかを研究しました (Fig. 6参照)。バイポーラトランジスタは、スイッチとしてオンにしようとすると少数キャリアの値が上がり、Fig. 6の中央図に示すように電流値が上昇します。t=tにおいて電流が一定値に達するとコレクタが接地電位となり、それ以上変化しなくなります。しかし、ベース側の少数キャリアは蓄積し続けるのです。Fig. 6の右図の初めのt=tの時点でデバイスのスイッチを切ろうとしても何も起こりません。ひたすら待ち続けるとこの時点で変化が起こり始め、さらにt経った後、スイッチとしてオフの状態に切り替わるのです。そこで、このデバイスは本当にデジタル回路を作る場合にはあまり向かないという結論に達しました。しかし、手元にあったのがそれしかなかったので、それを使ったのです。みんなそうでした。

Fig. 6

# 初期の研究――トンネル効果

私はこのテーマで学位論文をちょうど書き終えて、1959年にカリフォルニア工科大学の教員になりました。その頃、日本から江崎玲於奈(Fig. 7)が大学を訪れ、セミナーを受けることができました。彼は、少数キャリアを使わない電子トンネル効果で動作するデバイスを発明したところでした。私は一生足りるほど十分な少数キャリアがあるだろうと思っていたところでしたので、とても感激しました。これをきっかけに電子トンネルの量子現象の研究を始めました。

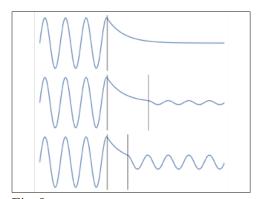

それは素晴らしいものでした。仕組みはこうです。具体的なケースをお話ししましょう。例えば、 雲母かそのようなものでできた非常に薄い絶縁体を用いたコンデンサを作るとします。両面に金属を 蒸着させます。こうしてコンデンサが出来上がりました。電子が金属の電極の中で大きな集団波動関 数を作っています。大きな巨視的な電子が一つあるようなものです。それが伝播すると電流が流れま す。もちろん、金属はそのように導体として働くわけです。しかし、縁体の表面にぶつかると波動関 数は絶縁体の中を伝播することができず、Fig. 8の上の図のように距離に応じて指数関数的に減衰して いきます。絶縁体が厚いと波動は絶縁体に跳ね返されるだけでどこにも行くことができません。しか し、Fig. 8の一番下の図のように薄い絶縁体にすると全ての波動関数が減衰するわけではなく、少しは 通り抜けて、もう一方の金属の中を伝播していきます。

つまり、コンデンサは電子が透過しやすくなり絶縁体を薄くすればするほどもっとそうなるのです。 非常に興味深いことでした。私たちの小さな研究グループは絶縁体や半導体の中での電子の挙動を測 定し、電子の波動関数をうまく取り扱えるまでになっていたのです。われわれは絶縁体の厚みを30オ ングストローム(3nm)まで薄くしました(Fig. 9)。それはもう素晴らしい時でした。

Fig. 7

Fig. 8

Reproduced by permission from Springer Nature: Mead, C.A., Some Properties of Exponentially Damped Wave Functions. In: Burstein, E., Lundqvist, S. (eds) Tunneling Phenomena in Solids, Plenum Press (1969).

https://link.springer.com/chapter/10.1007/978-1-4684-1752-4\_9

Fig. 9

## ゴードン・ムーア、そして集積回路との出会い

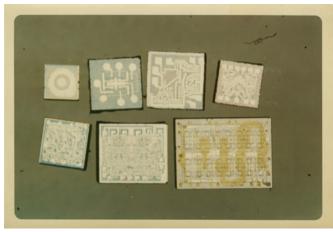

この頃、私はゴードン・ムーアのコンサルティングをしていました。彼が1960年にカリフォルニア 工科大学にやってきたとき知り合ったのです。彼らはフェアチャイルド・セミコンダクターという会社を設立し、とても素晴らしいトランジスタを製造していました。ある日、私はコンサルティングのためにフェアチャイルド社に行ったところ、彼が「カーヴァー、君に渡したいものがある」とこのような小さな展示物をくれました(Fig. 10)。

これはシリコンウエハです。直径は1インチです。1950年代から60年代初頭まではそれが標準的な大きさでした。これらは、最初の商用集積回路を作る工程の中でさまざまな段階にあるウエハです。これは歴史的価値のあるものです。まず、Fig. 10の一番左上にあるようなウエハがあって、それを研磨します。研磨されたウエハもその当時は、この写真の右上にあったのですが、一度実験に必要だったことがあり、使ってしまって戻せていません。次は、ウエハを酸化させ、n型にしたい部分の酸化膜に穴を開け、n型の不純物をシリコンに注入します(2列目右)。そしてまた酸化させ別の穴を開けp型不純物を注入します(3列目左)。ここではまだバイポーラトランジスタを作っているので、これがバイポーラトランジスタのベースとなります。次に、もう一度酸化させ穴を開け、再びn型不純物を注入してトランジスタのエミッタを作ります(3列目右)。これでnpn型トランジスタの完成です。最後にもう一度酸化させコンタクトを作りたい場所に再び穴を開けます。そして全体に金属をつけ一番右下に示すような小さな配線パターンになるようにします。これが集積回路です。

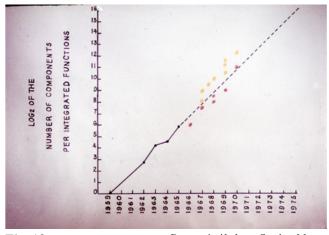

Fig. 11の上段左から二つ目の集積回路は一番シンプルなものです。これは、1965年にゴードン・ムーアが私にくれた写真です。上段一番左にあるトランジスタは1959年に彼らが作っていたトランジスタです。そして、その右にあるのが、最初の商業用集積回路です。時が経つにつれて彼らは、集積回路についてより優れた方法を考案していきました。より高度なもの、より複雑なデジタル機能を実現するためには、より多くのトランジスタが必要でした。そこで、より多くのトランジスタを一つのチップに搭載する方法が考え出されました。そして、1965年までにはこの写真に写っているものを全て完成させ、さらに彼はあることを思いつきました。

Fig. 11

Personal gift from Gordon Moore

### ゴードン・ムーアからの問い

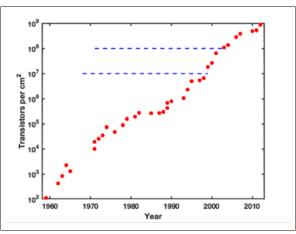

Fig. 12の黒い点は、チップに搭載されたトランジスタ数の対数を年度ごとに示したものです。これ は、現在「ムーアの法則」と呼ばれている1965年の彼の有名な論文に登場するものです。そして、こ の非常に太い破線を引き、年を追うごとに新たな集積回路のトランジスタ数を追加し続けたのです。 これはとても興味深い現象でした。その時、彼は私に言いました。「カーヴァー 、君は電子のトンネ ル効果を研究しているが、これはものが非常に小さくなったときに起こる現象だ。うまく作動するト ランジスタの最小サイズを制限してしまわないか」、私は「そうだ、間違いなく制限する」と答えまし た。彼は「では、どれくらいまで小さくできるのか」と尋ねました。私は「難しい質問だけど、一つ だけわかっていることは30オングストロームの厚さまでの絶縁体は作れるということだ」と答えまし たが、これは私たちのトンネル効果に関する実験のプロットからもわかることでした。そして、その ようなものを作り測定したのです。電流は少し漏れていましたが、悪くはありませんでした。

これは、30オングストロームの厚みの酸化膜を用いたトランジスタを使わない理由にはなりません。 しかし、当時人々が使っていた酸化膜は1000オングストロームもの厚みでした。つまり、1次元では30 倍、2次元の密度としては1000倍でした。1968年頃、このような議論をしていましたが、そこからは長 い道のりでした。この年はDevice Research Conferenceに招かれて、講演をした年でした。これは小 さな会議でしたが素晴らしいものでした。この会議は毎年IEEEが開催していて、固体デバイスの最先 端の研究をしている人たちを招へいしていました。研究者が一堂に会し、互いに最新の研究成果を聞 き議論するという素晴らしいものでした。そこで講演の依頼があり、私はゴードン・ムーアの問題、 つまりトランジスタをより小さく作るとどのような動作が確認されるかということについて話すこと にしました。

Fig. 12

Personal gift from Gordon Moore

#### スケーリング則

Fig. 13はその講演で使ったスライドです。トランジスタを小さくする方法はたくさんありますが、私は最も簡単に実現可能な方法を選びました。Fig. 13の上の模式図はトランジスタを表しています。これはバイポーラとは異なるトランジスタです。ここにn型領域があり、図の左右の網掛け部分はn型領域で、左がソース、右はドレインと呼ばれています。その間にあるのは、上のゲートにより電位が制御されている領域で、図上部の網掛け部分のゲートはある種の金属でできています。つまり、これは金属-酸化膜-シリコンのデバイス、すなわちMOS(Metal-Oxide Semiconductor)で、私たちは今もこれを活用して暮らしています。MOSデバイスをどんどん小型化していく最もシンプルな方法はXYZ全ての寸法を同じ倍率で小さくすることです。話を簡単にするため2分の1にしてみましょう。1枚のシリコンに1個のトランジスタを搭載していたのが4個になります。電圧も小さくしたので電界は変化しません。すなわち、ソースからドレインに向かう電子の速度は同じになるわけです。しかし、進む距離は半分になります。つまり、トランジスタは2倍速くなるのです。従って、1枚のシリコン上で8倍の計算能力を得られます。これはすごいことです。しかし多くの人たちは、もしこれをやると電力が極度に大きくなり、シリコンが溶けてしまうのではと主張していました。しかし、そうではありません。このように電圧を下げることで、単位面積あたりの電力は不変を保てるのです。

実際、同じ電力、同じシリコンであれば、スケール因子の3乗に比例した計算が可能になるわけです。これはすごいことです。信じられません。もちろん、そこではみんなが大騒ぎしていました。その人々の中でただ一人、声を上げずに黙々と考えていたのが、私たちの携帯電話やパソコンに使われているランダムアクセスメモリ(RAM)を発明したロバート・デナードです。ダイナミックRAMは彼の発明です。彼もまた京都賞受賞者の一人です。彼はこの問題について考えていました。そして翌年、彼はこの問題をもう少し深掘りし、私の結論に基本合意する講演を行いました。つまり、一人は産業界、もう一人は学界にいる私たち二人が、この種のスケーリングは有効でどのような物理法則にも反しないと確信を持つに至りました。ものを小さくしすぎるととんでもないことが起こるという論文は当時数多くありました。

1968年当時、私はものを1000分の1にコンパクトにしてもなんら物理法則に反せず、シリコンの単位 面積当たりの消費電力も同じであると言っていたのです(Fig. 14)。その会議からの帰り道、私は自分 の人生が永遠に変わってしまったと直感で思いました。問題はもはや「どのようにしてより優れたトランジスタを作るか」ではなく、「1000万個の可動部品があるものを作ってどうやって動作させるのか?」だったのです。これは大変な問題です!

Fig. 14

# インテルの設立と初の商用マイクロプロセッサ

1968年はいろいろな意味で分水嶺となる年でした。私は1960年からゴードン・ムーア(Fig. 15左)とボブ・ノイス(Fig. 15右)のコンサルティングをやっていました。その頃私たちは良き友人でした。

ゴードン・ムーアから連絡があり、「フェアチャイルド社を辞めて、集積回路を作るための新しい小さな組織を立ち上げるからコンサルタントとして参加しないか」と誘われました。彼の頼みは断れないので、NMエレクトロニクス社の5番目のメンバーとなりました。しばらくしてアンディ・グローブも加わり、彼がインテルという名前を考え出しました。そして、ご存知の通り世界でも有数の大企業になりました。これが変化の始まりでした。私はコンサルタントとして、彼らが集積回路用のマスクをどのように設計し、製造するかを見ることができました。

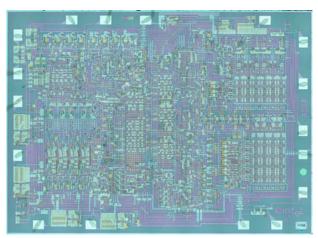

Fig. 16は、おそらくインテルの歴史の中で最も有名な回路の一つであるマイクロプロセッサ4004です――最初の商用マイクロプロセッサで1997年京都賞にも選ばれました。しかし、これはたかが4ビットのマイクロプロセッサに過ぎません。それほど高性能なものではありません。しかも、見てみると恐ろしく複雑なパターンになっています。では、そのようなものをどうやって設計するのでしょうか。特に、どうやってパターンを作り、どう組み合わせて、その機能を実現させるのでしょうか。簡単なことではありません。

Fig. 15

Gordon Moore and Robert Noyce at Intel in 1970

by IntelFreePress is licensed under CC BY-SA-2.0

Fig. 16

http://alumni.media.mit.edu/~mcnerney/2009-4004/4004-composite-photo.jpg, CC-BY-SA-3.0

# 従来のチップの設計法

そこで、彼らがどのように行ったのかを観察しました。まず、どのような仕事をさせたいかという機能の記述をします。次に、その中でお互いにどう関係しているかという論理関数の記述をします。そして、それをもとに別の人が、論理関数として記述された論理を実現するように接続されたトランジスタの電気回路図を作成します。さらにほかの人が製図機を使って、大きなマイラーフィルムの上に集積回路のレイアウトの全要素を網羅した巨大な図を描くのです。そうして出来上がるのが、さまざまな層が含まれた合成図なのです。次は、それぞれの層について順番にパターンを生成するために、各層ごとのマスク・マスターが必要になります。それは次の通り作成していました。

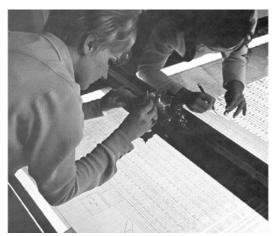

この写真(Fig. 17)のライトボックス全体にあるマスター図の上に、ルビリスと呼ばれるものを載せました。ルビリスはマイラーに非常に薄い透明な赤いコーティングを施したものです。コーティングはカミソリの刃で切り取ることができるほど薄いので、赤いコーティングを残したくない箇所の輪郭を切り取ることができます。この図では、高価なライトテーブルの上に設置される大きくて高価な座標展開機と呼ばれる非常に精密なものを用いて、カミソリの刃をX方向とY方向に移動させて正確な座標へと誘導します。そして、取り出したい部分の輪郭を切り取ったら、別の人がピンセットを持ってやってきて、切り出す部分以外の赤いフィルムの部分を傷つけないようにしながら慎重に赤いフィルムを剥がします。これは正気の沙汰ではありません!トランジスタが数千個の集積回路でこれをやるだけでも大変なのに、それを何百万トランジスタの集積回路でもやるとは頭がおかしくなりそうです!もっと良い方法があるはずでした。そのため、私はやらなければならなかったのです。絶対に自分で集積回路を作らなければならなかったのです。なぜなら、それこそが未来への道だったからです。

従来のやり方でやるわけにはいかなかったのです。しかし、もっと良い方法があることがわかりました。当時としてはずっと良い方法でした。

Fig. 17

# 新しい方法論――コンピュータによるパターン生成

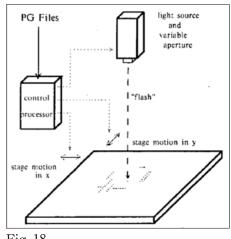

Fig. 18はガーバープロッタと呼ばれる装置の小さな図面です。ライトヘッドには光源が入っていて、その前に開口部があり感度の高い感光材に焦点を合わせることができます。焦点の位置はX方向とY方向に動かすことができ、光線の形や強さ、XとYの動きの三つを人間の手を借りずに全てコンピュータで制御できます。これは大量に処理するための方法です。このパターンジェネレータのファイルを生成するコンピュータ・プログラムを書けば、チップの図形情報(ジオメトリー)に合った任意に複雑で、精密なマスターを作ることができます。これは私にとって決定的に大きな発見でした。良い方法があったのです。

Fig. 19は小さなテストチップのメタルマスクを作図したものです。これは最終的なチップの大きさの250倍のサイズです。これで、私は集積回路を作るためのマスク・マスターを作成する方法を手に入れたわけです。そして、これを使ってマスク製作所で、ファブと呼ばれるウエハ製造システムで使えるマスクに仕上げたのです。

しかし、マイクロプロセッサ4004のような設計を見ると、その図形情報(ジオメトリー)を生成する プログラムを書くのは、手で描くのと同じくらい大変なものです。何百万個もの部品があるようなも のをどう設計したらいいのかはまだわからなかったのです。

これらをよく調べれば調べるほど、複雑なのはトランジスタではなく、それらの接続方法にあるということがわかってきました。信号がこのトランジスタからあのトランジスタに到達しなければならないとか、なんとかそこまでいかないといけないとか、ほかの全てのものと干渉してはならないとか、そういった要件のせいで複雑になっているのです。そこで、まず情報の流れについて考え、システム内でどのように情報が流れていくのか、全体像を捉えてはどうかと考えました。そして、その情報がほかの情報と相互作用しなければならない場合、その情報はどこから来て、どこへ行くのか、また、それらが互いに接続されていることを確かめることにしました。

そして、それに基づいて機能するブロックを設計し、情報のやりとり(通信)に適合した配線を作ります。これもまた飛躍的に大きな発見でした。

Fig. 19

Fig. 18

#### 最初のチップ

Fig. 20が私の最初のチップですが、そのような考え方から生まれたものです。このチップには二つのロジック・アレイがあります(Fig. 20左図)。左側のアレイは入ってきた入力を受け取ります。左側アレイの下にあるのが入力用のドライバーで、ここから左のアレイの垂直方向にラインが走っています。そこにある水平のラインは、任意のAND関数を形成するために先程の垂直の入力に接続されます。

これらのラインは右側のアレイに通じていて、そこには垂直のラインがあり、そのAND関数から任意のOR関数を計算することができるのです。そして、このアレイの適切な場所にコンタクトを置くだけで、任意の論理関数を作ることができるのです。右のアレイの左下にある部分で出力の一部を取得して入力にフィードバックし、小さなシステムが最終状態と左図の下の方にあるメモリに保存されている情報から次の状態を計算できるようになっています。

これが一般的な順序回路(有限状態機械)になるわけです。これはとてつもない発明でした。テキサス・インスツルメンツ社で一人、ヒューレット・パッカード社で一人、そして私がそれぞれ独自に発明していたほどです。

当時、新入りの協力者だったスティーブ・コリーがこの装置を見て、コンピュータ・プログラムを作ってくれました。それは、Fig. 20の右図の小さな「1」(コンタクトを置く位置)を用いてシステムが行う動作をシミュレーションするものでした。もちろん私は、このメモリを持った有限状態機械を作るための図形情報(ジオメトリー)を生成するガーバープロッタのコードを書きました。

そのコードを、ここロサンゼルスにある私のお気に入りの製作所に持ち込みました。するとそこの人がガーバー・マスター (基本設計図)を作ってくれました。そのガーバー・マスターをマイクロマスク社というインテル向けのマスク製造工場に持っていきました。そこでインテルのファブに合うマスクを作ってもらいました。当時インテルにはかつて私の学生だったジェリー・パーカーとテッド・ジェンキンスがいましたが、彼らが私のチップを試作製造ラインに流してくれました。そして私の元にチップが戻ってきました。

ある土曜日の朝、私は小さなパッケージにチップを貼り付けて(Fig. 21)小さな蛍光ディスプレイに直接、接続しました。そうするとシミュレーションと全く同じ動きを見せたのです。つまり、これは概念的な定義から生まれた物理的なものなのです。それが集積回路なのです。私は、人の手で図を描く必要がなく、またルビリスからフィルムを剥がす必要もない、そのような方法をとっていたのです。何百万トランジスタという規模に対応できる、練り上げられた設計方法だったのです。

Fig. 21

Fig. 20

# マルチプロジェクト・チップ

もちろん学生たちは、これが実際に動くという事実に気付いていたので作る方法を学びたがっていました。Fig. 22が初年度の授業の様子です。初回には実際に8人の学生がいました。当時、私はEE281という半導体デバイスの講座を受け持っていました。そこで私は、半導体デバイスとは何かを再定義しました。それはみんなが思っていたよりずっと複雑でしたが、私はチップ設計の方法を学生たちに教えました。

私が学生たちに教えたのは、まさに過去3年間にどうやって自分のチップを設計するかを考え、学んだことと全く同じことでした。各プロセスやステップ、そしてそれが図形的構造という観点ではどうなのか、電気回路図的にはどうなのか、論理としてはどうなのかといった概念をイメージすることができるかということでした。そのイメージを持てれば、すなわち全工程を頭の中に描くことができるのです。そして、一人でこの全工程をこなすことができるのです。私はそれをやりました。学生たちは私よりも賢いと思いますし、彼らも必ずできるようになるはずです。事実、彼らはやり遂げました。

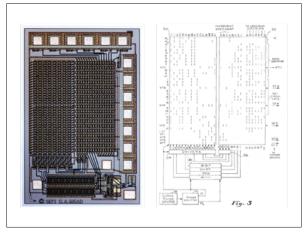

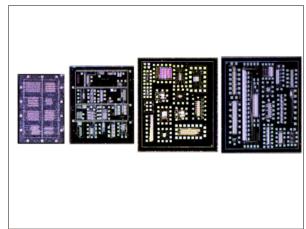

Fig. 23の左端のチップが初年度の講座で作ったチップです。もちろん、全ての学生のために異なるウエハでチップを製造することはできませんので、マルチプロジェクト・チップを作ることになります。チップ上にあるプロジェクトはそれぞれ学生のプロジェクトです。学生たちは、自分たちのプロジェクトについて図形情報(ジオメトリー)を生成するコードを書きました。次に私が、彼らのプロジェクトをマスターチップに落とし込むコードを書きました。そして、この写真からもわかるように、私たちは一緒に集まって、どのプロジェクトも互いにショートしないようにしました。

それから製作所の友人のところに行って、製造用のガーバー・マスターを作ってもらい、それを持っていきました。そして、マイクロマスク社がマスクを作ってくれて、ジェリー・パーカーかテッド・ジェンキンスがそれをインテルのファブで製造してくれたのです。1972年の1月にはチップを完成させ、私はそれをパッケージングしました。次に、学生はそれぞれパッケージ上のピンと自分のプロジェクトのパッド(端子)をつなげました。彼らは自分のプロジェクトの電極パッドがどこにあるか、パッケージ上のどのピンに端子を持っていきたいかを知っていたので、そうすることができたのです。接合が上手な者もいれば、なかなかうまくいかない者もいましたが、みんなうまく動きました。学生たちがそんなことをするのは無理だとは誰も言えなかったのです。なぜなら、学生たちは概念から、その概念を実現する実体まで作り上げたのですから。このマルチプロジェクト・チップ方式は、最初の学期に実際に自分のチップを持てるというもので、毎年行うようになりました。

私はこの講義の教え方を学んでいったので、ますます上手に教えることができるようになりました。 学生たちも、もちろん同じです。前年度の学生がティーチング・アシスタントとなったので、彼らは この作り方についてよく知っていました。ですから講義はどんどん良くなり、私はよりうまく説明で きるようになりました。Fig. 23の左から3番目のチップは1975年のチップです。この頃には、ほかに類 を見ない大変高性能な集積回路に関する学位論文を書いている大学院生が数人いました。そして一番 右の1976年のチップには、大きな縦長のものが見えますが、これはマイクロプロセッサ用の基本部品 となるビットスライスです。これはデイブ・ヨハンセンの学位論文のプロジェクトでした。

Fig. 22 Fig. 23

# 複雑な集積回路設計の新しいパラダイム

Fig. 24には、当時最先端だった16ビットのマイクロプロセッサのプロットとともに彼が写っています。このレイアウトは100%彼のシリコンコンパイラで生成されたものです。シリコンコンパイラとは1ワードに何ビット入っているとか、どんな機能を持たせたいか、というようなハイレベルの記述を取り扱うプログラムのことで、私たちが名付けたものです。そして、記述した仕様を全て実現するコードを生成する、これがコンパイラの仕事です。

実現したい機能が配置され、それらは全てバス(共通配線)でつながります。つまり、よく整った配線図のようなものです。そして、先ほどお見せしたようなロジック・アレイがあり、これにより機能に個性が生じるのです。つまり、ハイレベルの記述をするだけでさまざまなマイクロプロセッサを作ることができるのです。これが以後のマイクロプロセッサ設計の教科書的な例となり、この方法論は今日に至っているわけです。

Fig. 24

# リン・コンウェイとの共著の執筆: Introduction to VLSI Systems

さて、この頃、当時コンピュータ科学の分野でかなり注目されていたゼロックス社パロアルト研究所に招かれて講演をしました。そこで私は、私たちがここでやっていることについて話しました。講演の後、リン・コンウェイという女性に会ったのですが、とても聡明な女性でした。長々と会話した末、彼女は「カーヴァー、あなたはこれについて本を書くべきです」と言ってくれました。当時、私

は自分のことで精一杯でしたから、「本当にそう思うなら、あなたが共著者になって一緒に書きましょう」と返しました。それで私たちは実行しました。

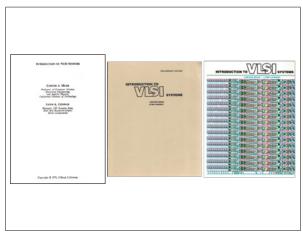

これが三つのバージョンです(Fig. 25)。一番左は1978年のプレプリント版、中央は79年のプレプリント版、そして一番右の実際の本は80年に出版されました。

Fig. 25

# どのようにマルチプロジェクト・チップが広まったか

そしてこのような流れになりました(Fig. 26)。これらは序文から抜粋したものです。私たちは1977年に作業を始め、秋までに最初の3章を完成させ、私はそれを講義で使えるようにしました。実際、カリフォルニア大学バークレー校のカルロ・セークィンは彼自身の講義で使用しました。そして1978年には、ゼロックス社が引き受けてくれたプレプリントは、実際にアメリカや世界中の四つの異なる場所で使われるようになりました。しかし、1979年に大きなことが起こりました。リン・コンウェイが優秀な人材を集め、その多くがこの地域の出身者でしたが、集積回路の設計やロジスティクスの面で非常に有効な体制を整えました。

彼女はMPC79というものを催し、世界中の大学にチップの設計を提供するよう呼びかけました。そして彼女はARPAからARPANET(まだインターネットになる前の時代でした)の使用許可を得て、それを用いて彼らの設計を集めたのです。フェアチャイルド社時代からの古い仲間だったパット・カストロが、当時ヒューレット・パッカード社のファブを担当しており、彼らがボランティアで製造を行ってくれました。その後、私たちがカリフォルニア工科大学でやっていたのと同じく、1月にチップを送り返してくれました。ここ、カリフォルニア工科大学から生まれた講座はこうして世界中に広まったのです。それ以降のことは広く知られている通りです。

Work on this text began in August 1977. The first three chapters were used as course notes during the fall of 1977, in courses given by Carver Mead at Caltech and by Carlo Sequin at U C. Berkeley. This present printing is being used during the spring of 1978 in courses given by Ivan Sutherland at Caltech, Robert Sproull at Carnegie-Mellon University, Dov Frohman-Bentchkowsky at Hebrew University, Jerusalam, and Fred Rosenberger at Washington University, St. Louis.

In fall 1979, Lynn Conway and her colleagues at Xerox PARC organized MPC79 the first multi-university multi-project chip. 124 designers from universities around the world contributed 82 chip designs in CIF2.0 format over the ARPAnet. Pat Castro at Hewlett-Packard (Palo Alto, CA, USA) agreed to donate wafer fabrication, and the packaged chips were shipped back to the designers in January 1980.

"An atmosphere of excitement and anticipation pervades this field. Workers from many backgrounds, computer scientists, electrical engineers, and physicists, are collaborating on a common problem area which has not yet become classical. The territory is vast, and largely unexplored. The rewards are great for those who simply press forward."

Fig. 26

# 結び――よりつながった世界

さて、皆さんはこの夜の地球の写真を見たことがあると思います(Fig. 27)。

この光の点の一つ一つにいる人は、ほかの光の点にいる人と潜在的につながっていることを思い出してください。私たちはものすごく広範囲につながった世界に住んでいます。また、これは私が1952年にカリフォルニア工科大学に入学した時とは全く違っています。1959年に私が教員になった時ともまた違っています。

私の考えでは、よりつながった世界は、より賢明な世界へ至るための最初の前提条件となります。幸いにして、私は長年にわたってこの進化の過程に貢献できる機会に恵まれてきました。そして、私の学生、共同研究者や同僚、この偉大な変化を可能にした世界中の人々を代表して、エレクトロニクス分野で今年の京都賞を受賞することを大変深く光栄に思います。

Fig. 27

NASA Earth Observatory/NOAA NGDC