| 題名               | 創造への途(みち)―私の開発者人生―                                      |

|------------------|---------------------------------------------------------|

| Title            | Reflections on Creativity in My Microelectronics Career |

| 著者名              | ロバート・ヒース・デナード                                           |

| Author(s)        | Robert Heath Dennard                                    |

| 言語 Language      | 日本語·英語 Japanese, English                                |

| 書名               | 稲盛財団:京都賞と助成金                                            |

| Book title       | Inamori Foundation: Kyoto Prize & Inamori Grants        |

| 受賞回              | 29                                                      |

| 受賞年度             | 2013                                                    |

| 出版者              | 公益財団法人 稲盛財団                                             |

| Publisher        | Inamori Foundation                                      |

| 発行日 Issue Date   | 8/20/2014                                               |

| 開始ページ Start page | 104                                                     |

| 終了ページ End page   | 140                                                     |

| ISBN             | 978-4-900663-29-9                                       |

|                  |                                                         |

# 創造への途 一私の開発者人生一

# ロバート・ヒース・デナード

今回、このように皆様にお話をさせていただく機会をいただいたことを大変嬉しく思います。本日は、まず私の人格形成期として幼い頃や学校のお話をさせていただいた後、マイクロエレクトロニクスの世界に飛び込んでからの最もクリエイティブだった時代を振り返ると共に、長い年月を経てマイクロエレクトロニクスという技術が今日のように社会に大きな影響を与えるに至った経緯についてお話をさせていただきます。締めくくりとして、2000年に依頼を受け、新たな世紀ならびに千年紀における機会とチャレンジについて「創造性」という切り口から私の考えをまとめた拙文に手を加えたものを披露させていただきます。

# 人格形成期

私は1932年、世界大恐慌の真っただ中にテキサス州の小さな町で生まれました。両親はあまり裕福ではありませんでしたが、誇りは高く、子供にも愛情を持って接してくれました。私の物心がつく前、家族はテキサス州東部の田舎の小さな農場に移ったのですが、その家にはまだ電気が来ていませんでした。父は畑を耕しながら家畜を育て、母は家族の食事を作り、洗濯をしてくれていました。私が初めて通った学校の校舎には教室が1つしかなく、1年生から3年生が学年毎に机を並べて勉強していました。数年後に私はそこよりも少し大きな学校に移ったのですが、その学校でも4年生の私のクラスは5年生と同じ教室でした。学校の勉強は難なくこなせたので、私は上級生のクラスを聴講したりして、自分にあったベースで勉強を進めることを許してもらっていました。その頃には姉と兄はすでに成人して家を出ていたのですが、実家には頻繁に帰ってきており、私にとっては素晴らしいお手本となりました。長い夏休みには、たっぷりの自由時間を利用して、考え事をしたり一人で遊んだりしていました。

1940年代初頭に第二次世界大戦が勃発したのをきっかけに、父はダラス郊外の小さな町に引っ越しを決めました。私も大きな学校に通いだし、クラスメートとお互い刺激し合える雰囲気の中で過ごしました。また、その町には図書館もありましたので、私は熱心に本を読むようになりました。

姉のエバンジェリンは、従軍看護師を志して家を出る時、自分の蔵書とレコード盤を置いていってくれました。私が特に感銘を受けたのは、大判で赤いカバーのSF傑作短編集でした。どの物語も楽しく読めたのですが、特にH・G・ウェルズの作品群には若いイマジネーションを掻き立てられ、いつしか頭の中には奇妙な世界や人々の

# Reflections on Creativity in My Microelectronics Career

# **Robert Heath Dennard**

I am very happy to have this opportunity to speak to you. I will talk first about my formative years, my childhood and my education, and then about my most creative years in microelectronics and how microelectronics evolved over the years to have such an astounding impact on society. I will close with an update of an essay on Creativity I was invited to write in the year 2000, looking at opportunities and challenges for the new century and beyond into the new millennium.

#### The Formative Years

I was born in a small town in Texas in 1932, in the middle of the Great Depression, to a loving family of very modest means, but great pride. By the time I was growing up, we had moved to a small farm in a rural area in East Texas and lived in a house which did not yet have electricity. My father farmed the fields and raised the livestock, while my mother kept us fed and provided with clean clothes. I started my education in a one room schoolhouse with three grades in different rows of desks. After a couple of years I moved to a little larger school where my fourth grade class was in the same room with a fifth grade class. Learning came easily to me, so I had a chance to hear what the higher grades were doing and advance at my own pace. My older sisters and brother had grown up and left home, but they visited frequently and provided great role-models. I remember long summers with a lot of free time to think and entertain myself.

In the early 1940s when World War II came, my father saw an opportunity to move our family to a small town just outside Dallas. I now attended bigger schools and lived in a community where I could visit and interact with classmates. I also found the library and became an avid reader.

When my sister Evangeline went away to become an army nurse, she left behind her collection of books and phonograph records. I was totally impressed with a large red book which was an anthology of science fiction short stories. I read them all with pleasure, and I particularly enjoyed those by H.G. Wells which stimulated my young imagination and formed vivid images of strange worlds and people. I was very amused by a book of Ogden Nash poems which I read and memorized. There was also an album of Sigmund Romberg operettas which fascinated me. I sang along with them and also memorized the words and tunes. This most likely was the starting point for my love of choral singing and all forms of music.

While I loved sports, and played baseball and touch football with my friends, I was not big enough or fast enough to compete in high school team sports which were 鮮明なイメージができあがっていました。また、オグデン・ナッシュの詩集も大好きで、暗記してしまうほどでした。レコード盤ではシグマンド・ロンバーグのオペレッタ選集がお気に入りで、一緒に歌ったりしていたので、歌詞とメロディーを覚えてしまいました。私が今でもコーラスやジャンルを問わず音楽が好きなのは、どうやらこの頃にルーツがあるようです。

一方、スポーツも好きで、子供の頃は友達と一緒に野球やタッチフットボールをして遊んでいました。高校ではチームスポーツが大切だと問囲からことあるごとに聞かされていましたが、私は高校のチームでプレイするほど体も大きくなく、足も速くはありませんでした。幸いなことに、高校2年生の時に音楽クラブができ、私はそちらに参加することにしました。最初に担当した楽器はフレンチホルンだったのですが、マーチングバンドにバスホルンが必要だということで、その後バスホルンに持ち替えました。

高校も卒業が近くなってくると進路を決めなくてはならず、進路指導の先生と相談した結果、電気技師になろうと決心しました。先生は、電気技師の仕事はこれから急速に伸びていくだろうし、私には数学の適性もあり、科学にも興味があるようだから向いているのではないか、と言って薦めてくれました。それで私はたくさんの友達と一緒に近くの州立短期大学に進もうと考えていました。

ここでその後の人生をすっかり変えてしまうことになる出来事が起こりました。ダラスの南メソジスト大学のバンド・ディレクターが私を訪ねてきて、奨学金を出すから州立短期大学よりもずっとレベルが上の南メゾジスト大学のバンドに加わらないか、と誘ってくださったのです。その方は私に「自分に与えられた最高のチャンスを活かすべきだ」と話されました。この言葉に私は衝撃を受け、それからというものは忠実にその言葉に従い、その後も南メソジスト大学から、現在はカーネギーメロン大学として知られる技術系の名門校であるピッツバーグのカーネギー工科大学へと進みました。また、当時、トーマス・J・ワトソン研究所を立ち上げたばかりのIBMに就職するチャンスを得た時も、私は躊躇しませんでした。

# クリエイティブな時代

1960年代の半ばには、私も研究者として独り立ちし、幸運にもマイクロエレクトロニクスの世界と関わりを持つようになりました。ここからは、今回の受賞の対象と

heavily emphasized. Luckily in my sophomore year a high school band was started and I became a member. I played French horn at first, and later I switched to a bass horn which was needed in the marching band.

As I was finishing high school, I chose my future career as an electrical engineer with the help of a guidance counselor. She advised me that electrical engineering was a fast-growing field and she said it would be good for me because of my mathematics aptitude and my interest in science. I planned to go to a nearby state junior college along with many friends.

One day an important thing happened which changed my life. The band director at Southern Methodist University in Dallas came to visit me and offered me a band scholarship to come to this much better school. His advice was "Why not take the best opportunity available to you." That was a striking idea to me that helped guide the rest of my life. It helped me go on from SMU to Carnegie Institute of Technology in Pittsburgh, a top engineering school which is now Carnegie Mellon University. And from there, when I got an opportunity to join IBM at the time its Thomas J. Watson Research Center was just being started, I didn't hesitate.

#### The Creative Years

After a learning period in research, I feel very lucky that I got involved in microelectronics in the middle of the 1960s. I would like to tell you something about the invention for which I am being honored, how it came about, and where it fits in the broad context of microelectronics.

This chart (Fig. 1) by Prof. Sah, a pioneer of the field, defines three different phases of microelectronics. Phase I includes the invention of the transistor and its early use as a discrete device replacing a vacuum tube. Phase II began with the concept of the integrated circuit, using micro-imaging techniques to fabricate many transistors, other components, and the wires connecting them together on a tiny silicon chip. Ten years were taken to develop this technology and actually make it work. The third phase beginning in 1969 saw the development and continuous improvements in microelectronics, which has continued ever since.

I got involved in the second phase of microelectronics in the middle of the 1960s. I was assigned to work in a group at IBM Research which was developing a new kind of transistor, called a field-effect transistor. These transistors were also called MOS transistors for Metal-Oxide-Semiconductor. That name describes their structure: a metal

#### Chronology of the Microelectronics Era

- Phase I, 1926-1957, Discovery

Rudimentary Semiconductor Device Concents

- Phase II, 1958-1968, Basic Technology and Transistor Innovation

- Early Integrated Circuits

- Control of Silicon Surface and Insulators

- Phase III, 1969- , Integrated Circuit Production

Commercial Applications

- Continuous Evolution of Capability

(After Prof. C.T. Sahi

Fig. 1

なった発明とその発明の背景、さらにマイクロエレクトロニクスという大きな枠組み の中におけるその発明の位置づけについてお話ししたいと思います。

この分野の草分け的存在であるサー教授は、マイクロエレクトロニクス発展の歴史 を3つの時期に分けています。トランジスタの発明とその黎明期における真空管に 代わるディスクリート・デバイスとしての利用が第1期です。第2期は、小さなシ リコンチップ上にトランジスタなどの部品を形成し配線接続する集積回路のコンセプ トの誕生で幕を開けます。この技術の開発および実用化には10年を要しました。第 3期は1969年から現在に至るまで連綿と続く、マイクロエレクトロニクス技術の発 展と継続的な改良です(Fig. 1)。

私がこの世界に関わるようになったのは1960年代半ばですから、第2期というこ とになります。当時、私はIBM研究所内で、電界効果トランジスタという、新しい トランジスタの開発を行っていた研究グループに配属されました。このトランジスタ は、金属酸化膜半導体トランジスタで、略してMOSトランジスタと呼ばれます。こ の名前は、半導体基板上の薄い酸化絶縁膜の上に金属ゲートを形成するという構造か ら来ています。特に私の小グループでは、どうすればこの新しいトランジスタが、シ リコン基板上に構築された集積回路においてコンピュータとしての機能を果たすよう にできるのかを研究していました。

大きな目標としては、当時ランダム・アクセス・メモリ(RAM)に使われていた磁 気コア技術の置き換えを実現することでした。磁気コアメモリは、ビーズにそっく りの小さな磁性体リングをワイヤで数珠繋ぎにし、大型の2次元アレイとして平面 的に配置したものです。これらのビーズーつ一つは磁化することによって1ビット のデータを記憶することができます。当時、IBMで最も大きかったメインフレーム

gate over a thin oxide insulator on a semiconductor substrate. My particular small group had the task of learning how to use this newly emerging type of transistor in integrated circuits, built on silicon substrates, to perform computer functions.

The big goal was to replace the magnetic-core technology used in those days for Random Access Memory (called RAM). In those memories small loops of magnetic material, very much like beads, were strung together using wires into large twodimensional arrays. Each of these beads could be magnetized to store one bit of data. The largest memory in the largest IBM mainframes at that time was 1 megabyte, the clock rates were 100s of kilohertz, and the power consumption was 40 kilowatts. We had a proposed way to build memory with our MOS technology which used six transistors in a flip-flop memory cell to store each bit. We hoped to integrate 128 of these memory cells in a small silicon chip.

One day in late 1966 an important event in my life occurred. During the day l attended a large IBM Research conference where various projects were presented. I was very impressed by a description of a proposed thin-film magnetic memory, which was projecting hundreds of thousands of bits in a 25 cm wide memory board. What impressed me as fundamentally better about their approach was that they had a very simple memory cell, just a small square of magnetic material at the intersection of two etched copper lines. I was inspired to find something that simple for the technology we were developing.

I went home that evening pondering analogies between magnetic circuits and electronic circuits. I considered the possibilities for using a simple capacitor as a basic memory element, storing a bit of binary data by charging or discharging the capacitor to two different voltage levels.

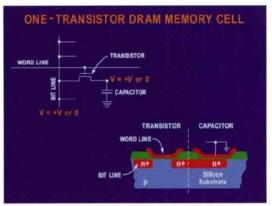

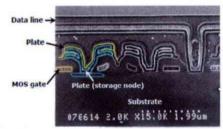

This slide (Fig. 2) shows the simple circuit I discovered. A capacitor, as suggested by its symbol, is just two conducting plates separated by a thin insulator. I found that an MOS transistor in series with each capacitor could be used as a switch to connect the capacitor to a data line briefly to charge or discharge it to write a data bit, represented by a positive voltage level, +V, or a zero voltage level on the bit line. The transistor is turned on and off by a control signal on a word line which allows selecting a given capacitor from many others for receiving the data on that bit line.

In my initial thinking the capacitor was the gate of another transistor, and reading was accomplished by monitoring the current flow in that second transistor. I was very excited about this idea, but it wasn't as good as I wanted. It required multiple access lines, with complicated drive schemes or an additional transistor to make a memory

のメモリは最大1メガバイト、クロック速度は数百キロヘルツ、消費電力は40キロワットでした。私たちは、各ビットの記憶をつかさどるフリップフロップ・メモリセル1つに対して6つのトランジスタを使うMOS技術を利用してメモリを構築するという手法を提案し、小さなシリコンチップに128個のメモリセルを集積しようとしていました。

1966年末のある日、その後の私の人生を左右する出来事が起こりました。その日、私が出席したIBMの研究部門の大規模な会議で様々なプロジェクトの発表が行われました。その中の、薄膜磁気メモリに関する発表に大きな感銘を受けたのです。幅25センチのメモリボードに数十万ビットを搭載するというものでしたが、彼らのアプローチの方が基本的に優れていると思ったのは、エッチングした2本の銅線が交差するところに角型の小さな磁性体を配するというごくシンプルなメモリセルを使用していた点です。私たちが取り組んでいる技術にもこのようなシンプルなものを使うべきだ、と大いに刺激を受けました。

その晩、家に帰った私は、磁気回路と電子回路の類似点について考え抜きました。 そして、シンプルなコンデンサを基本記憶素子として使用し、コンデンサを2段階 の電圧レベルになるように、充電あるいは放電することで、1 ビットのバイナリデー タを記憶できないものかと考えたのです。

このスライドは私が考案したシンプルな回路を示しています(Fig. 2)。回路図上の記号からも分かるように、コンデンサは導電性のプレート2枚に薄い絶縁体を挟んだ構造をしています。各コンデンサと直列に繋いだMOSトランジスタをスイッチとして使い、コンデンサはデータ信号を扱うビット線に繋いで、短時間の充電あるいは放電をすることで、ビット線上で正の電圧レベル(+V)もしくは零電圧レベルとして表わされるビットデータを書き込むことができることが分かりました。トランジスタのオン/オフは、ワード線上の制御信号で行いますが、これにより多くのコンデンサから特定のコンデンサを選んで、そのビット線上のデータを受け取ることが可能になります。

最初の考えは、コンデンサをもう1つのトランジスタのゲートとし、読み込みは そのトランジスタに流れる電流をモニターすることによって行う、というものでし た。このアイデアはとても気に入っていたのですが、思ったほどにはうまくいきませ んでした。アクセス線を何本も使うため、複雑な駆動方式が必要だったり、メモリア レーを正常に動作させるためにトランジスタがもう1つ必要だったりしたためです。

Fig. 2

array function properly. I kept working on various configurations for a few weeks until I finally realized that the stored charge could be read back out through the same transistor through which it was written, which would create a small detectable signal on the bit line. The cell had been reduced to a single transistor and a capacitor at the intersection of two access lines. I was satisfied that this was as close to my goal as possible, and offered a great reduction in complexity compared to the six-transistor memory cell.

The drawing below shows a cross-section of a field-effect transistor and a capacitor forming a one-transistor memory cell. I won't attempt to describe this in detail. A beauty of the integrated circuit is that the conducting layer forming the gate of the transistor is common to all the gates so it also serves as the wire selecting a particular row of cells. Also, one doping region in the silicon is both the drain electrode of the transistor and as one of the capacitor electrodes. A distinctive characteristic of this memory cell is that a small leakage current from this n-doped region to the p-type silicon substrate discharges the capacitor in a fraction of a second. This gives rise to the name "dynamic" since the data is only stored temporarily. To preserve the data it must be refreshed by reading it out and writing it back into each cell at certain intervals. Fortunately the speed of this memory scheme allows more than a hundred million read or write operations per second and only a small percentage of these are needed for refreshing the data. Thus this scheme became known as dynamic RAM, and commonly called DRAM.

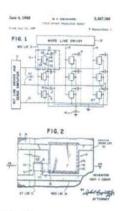

This slide (Fig. 3) shows a drawing from the U.S. patent which I was granted for this work in 1968. It shows a small array of memory cells connected to circuits for supplying the data and for selecting a particular row of cells. My management at IBM 2、3週間ほど様々な回路構成の検討をし続け、コンデンサの電荷は元々のデータを書き込んだトランジスタを介して読み出すようにすればビット線に検知可能な微細な信号が発生するので、読み出しが可能になるとようやく気付きました。セルはトランジスタ1つと、2本の配線の交差点上のコンデンサ1つにまで簡素化されました。トランジスタを6つ使ったメモリセルと比べ、複雑さを大幅に軽減したこのセルは、私の理想に最も近いもので、自分でも満足できるものでした。

下の図は、電界効果トランジスタ1つとコンデンサ1つで構成された1トランジスタ型メモリセルの断面図です。ここでは詳しい説明は省略しますが、集積回路の美しい所は、トランジスタのゲートを構成する導電層がすべてのゲートに共通しているので、特定のセルの列を選択する役目も果たしていることです。また、シリコン内のドーピング領域がトランジスタのドレイン電極と1つのコンデンサ電極としての役割を同時に果たします。このメモリセルの特長は、このn型にドープした領域からp型のシリコン基板への僅かな漏れ電流によってコンデンサの放電が一瞬にして行われるということです。このように、データは一時的にしか蓄えられないので「ダイナミック」という名前が生まれました。セルのデータを維持するためには、一定の間隔で読み出し、再書き込みを行うことでデータをリフレッシュしなければなりませんが、幸い、このメモリ方式は1秒間に1億回以上の読み出しあるいは書き込み操作が可能な速さを実現しており、データのリフレッシュには、そのうちの数パーセントを使うだけで済みます。このようなことから、このメモリはダイナミックRAM、一般にDRAMと呼ばれるようになりました。

この回路図(Fig. 3)は、今お話しした研究で1968年に私が取得した米国特許で使用したものです。データを供給し、セルの列を選択できるように、回路に繋がった小さなメモリセルが配列されているのが分かります。IBMの私の上司はこの新たな発明が持つ可能性を理解してくれましたが、当時はまだこの技術の採用にはリスクが大きすぎると判断しました。電荷の漏れが見られ不安定だったのです。そこで私は研究仲間数人と研究に戻り、6つのトランジスタを使ったセルで512ビットの試作品を設計し、実証を行いました。後に、このトランジスタを6つ使ったセルは「ダイナミック(動的)RAM」に対して「スタティック(静的)RAM」と呼ばれるようになりました。間もなく、私たちはMOSトランジスタの製造処理工程の開発を終え、設計マニュアルを仕上げ、生産部門に送りました。

Fig. 3

understood the potential of this new invention, but it was considered too risky for the technology at that time, which was still leaky and unstable. So, I went back to work with a few others to design and prove a prototype of a 512-bit chip using the six-transistor cell. Later on, this six-transistor cell came to be called "static RAM" after "dynamic RAM" was named. In time we completed the research and development work on the MOS transistor process, wrote up a design manual and transferred it to manufacturing.

Eventually, in the early 1970s IBM shipped the first computers with semiconductor memories using the more established bipolar transistor process, and the MOS static RAM won out in the next generation because of its greater density. In the same time period various versions of dynamic RAM began to appear in the industry, at first with several transistors per cell like the popular product from intel.

I finally got a chance to work on my one-transistor dynamic RAM scheme in 1970 when a new project was started at IBM Research with the ambitious goal of drastically reducing memory costs by combining the simplicity of one-transistor memory cells with a substantial reduction in all the transistor and wiring dimensions of the integrated circuits. My longtime associate Dale Critchlow was the leader of this program. We wanted to take advantage of dramatic advances in lithography techniques which were being developed at our laboratory – such as electron-beam pattern writing – which we felt could reduce the dimensions used in integrated circuits by a factor of five.

One of the practical problems we had to face was how to design MOS transistors with such very small dimensions. We knew that just reducing the size caused them to switch on and off poorly. My small group responsible for the MOS transistor design considered all of the problems and it soon became clear that there was a general way to

# Scaling Principles for MOS Technology

やがて、1970年代に入ってIBMは、技術的により確立されたバイポーラトランジスタ技術を用いて、半導体メモリを搭載した初めてのコンピュータを出荷したのですが、その次世代コンピュータには、集積密度の高いMOSスタティックRAMが採用されました。同じ頃、様々な形のダイナミックRAMが市場に出回り始めていました。最初は、インテルが商品化したような、セル1つに対して複数のトランジスタを使うものでした。

1970年、私はついに私の考案した1トランジスタ・ダイナミックRAMの設計を行う機会に恵まれました。IBMの研究部門が、シンプルな構造の1トランジスタ型メモリセルを採用すると同時に集積回路上のトランジスタおよび配線全体の寸法を大幅に縮小することでメモリのコストを劇的に下げる、という野心的な目標を掲げ、新しいプロジェクトを立ち上げたのです。長年の研究仲間であるデイル・クリッチロウがこのプログラムのリーダーでした。私たちは、電子ビームによるパターン描画など、当時、私たちの研究室で開発が進められていたリソグラフィー技術の飛躍的発展の成果を利用できないものかと考えました。これが実現すれば、集積回路で使用される回路寸法を従来の5分の1にまで小さくできそうだったからです。

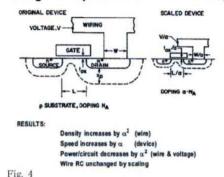

ここで私たちは、どのようにMOSトランジスタをそれだけ小さなサイズに設計するか、という現実的な問題に直面しました。単にサイズを小さくするだけではスイッチのオン/オフがうまくいかないことは分かっていました。私の下でMOSトランジスタの設計を担当していた小グループは、あらゆる問題を検討し、いくつかの鍵となるパラメータのスケールダウンなどによって、素子を小型化するための一般的方法があることを程なく突き止めました。次のスライドで説明します(Fig. 4)。

Fig. 5

design smaller devices which involved scaling down of a few key parameters. This is illustrated in the next slide (Fig. 4).

We found that reducing the applied voltage "V" and increasing the silicon substrate doping concentration "N", by a certain scaling factor "alpha", allows all the dimensions of the MOS devices to be reduced proportionally. The smaller transistor on the right has the same electric field patterns as the transistor on the left, so it behaves in a similar way and turns on and off properly. Also we planned to scale down all the interconnect lines by the same amount to get much denser integrated circuit layouts.

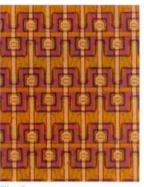

It was a remarkably simple and concise concept, yet very powerful. It told us our miniaturized circuits would switch faster and also use much less power. We built a lot of very small devices, scaled by a factor of five, to confirm the theory and to understand the limits. I presented this work at the International Electron Device Conference in 1972. Just a few months later at the International Solid-State Circuits Conference in 1973, several companies including IBM were showing the first early versions of memory chips using my one-transistor dynamic memory cell. The acronym DRAM (pronounced dee-RAM) came to be used for this type of memory. At the same conference my associate Dr. H. N. Yu demonstrated a small array of DRAM memory cells scaled 25 times smaller in area by using electron-beam pattern writing. Dr. Yu, along with me and other authors, followed up by publishing an entire experimental 8-kilobit DRAM chip with these deeply-scaled dimensions in 1975.

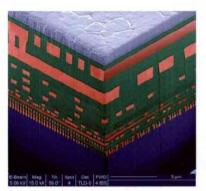

This slide (Fig. 5) shows a greatly magnified photograph of some memory cells in that chip. The light colored vertical shapes are the aluminum word lines. They are connected to small square features which are the transistor gates. The horizontal shapes

私たちは、任意のスケーリング因子「アルファ」を用いて、印加電圧「V」を下げると同時に、シリコン基板のドーピング濃度「N」を上げることによって、MOSデバイスの縦、横、高さのすべての寸法を同じ比率で小さくすることができることを発見しました。右側の小さい方のトランジスタの電界パターンは、左側のトランジスタと同じなので、左側のトランジスタと同様の動きを示し、問題なくオン/オフを行うことができます。私たちは、接続線もすべて同じだけスケールダウンし、はるかに集積度を高めた集積回路のレイアウトを実現しようと考えました。

このコンセプトは驚くほど単純かつ簡明ですが、非常にパワフルでした。小型化した回路は、スイッチングのスピードが上がるだけでなく消費電力も大幅に抑えることができました。私たちは5分の1サイズのデバイスを大量に作り、自分たちの理論と技術的な限界を検証しました。1972年にこの成果を国際電子デバイス会議(International Electron Device Conference)で発表したところ、わずか数ヶ月後に開かれた1973年の国際固体素子回路会議では、IBMを含む複数の企業が、私の発表した1トランジスタ・ダイナミック・メモリセルを利用したメモリチップの初期バージョンを展示していました。そしてこのタイプのメモリはその頭文字を取ってDRAM(ディーラム)と呼ばれるようになりました。また、この会議では私の同僚であるH・N・ユー博士が、電子ビーム露光技術を用いて面積を25分の1まで小さくしたDRAMメモリセルの小型アレイを披露しました。そして、1975年に彼は、私を始めとする開発陣と共に、この微細化技術を駆使した8キロビットDRAMチップの試作品の学術発表をしました。

この写真(Fig. 5)は、そのチップで使われているメモリセルを高倍率で拡大したものです。色の薄い縦方向のパターンはアルミのワード線で、小さな角形のトランジスタ・ゲートに繋がっています。そして横方向にあるのはビット線とコンデンサの上部電極です。

1976年に出版された日経エレクトロニクス誌の表紙です(Fig. 6)。右上にありますように、8キロビットDRAMに関する私たちの論文が掲載されています。

こちらがその「高集積密度8Kビット・メモリー・チップ」の論文の最初のページです(Fig. 7)。この論文を始めとする、微細化、すなわちスケーリングに関する私たちの研究は、「VLSI(超大規模集積回路)プロジェクト」と呼ばれる日本の大規模国家プロジェクト立ち上げの大きな原動力になったと言われています。このプロジェクトが持つ影響は大変大きく、私が最初に京都を訪れたのも「VLSI Technologyシン

Fig. 6

Fig. 7

are the bit lines and the top electrode of the capacitors.

This slide (Fig. 6) shows the cover of an issue of Nikkei Electronics in 1976 which contains a reprint of our 8-Kbit DRAM paper as described in the upper right corner.

This slide (Fig. 7) shows the first page of that reprinted paper about the deeply-scaled 8-Kbit DRAM chip. This paper and our related work on scaling have been cited as key factors in the establishment of a large national program in Japan called the "VLSI project" (for Very Large Scale Integration). The impact of that program has been huge. I first visited Kyoto to attend a Symposium on VLSI Technology, an international conference which is still held in Kyoto or Honolulu on alternating years.

Circuit design innovations also played an important role in the development of the dynamic RAM. The main difference between the dynamic RAM and the earlier static RAM was the need to sense very small signals coming from the memory cells onto the bit lines when a given word line was activated, and to write the original voltage levels back into the memory cells after this destructive read. For some time after my invention I had the notion that I would use off-chip bipolar sense amplifiers like we had used with our previous static-RAM chips. Even for the small arrays which were appropriate to the design groundrules of those days, the number of terminals which could be assigned to bit lines represented a big limitation.

We knew that on-chip sensing circuits were desirable, but there was very little experience with MOS circuits for sensing small voltages. The variations in the threshold voltage (the gate voltage required for turn-on) were quite large in those days. One day Dale Critchlow came around to discuss some balanced latch circuits he had heard about, which I believe were being used in touch-actuated keyboards to sense small

#### Open Bitline Architecture with 1T1C DRAM Cells

(K. U. Stein, et al., IEEE Journal of Solid-State Circuits, Oct. 1972)

Fig. 8

ポジウム」に出席するためでした。ちなみに、この国際シンポジウムは現在も京都とホノルルで毎年交互に開かれています。

ダイナミックRAMの開発には、回路設計のイノベーションも大きな役割を果たしています。ダイナミックRAMが初期のスタティックRAMと大きく違うところは、任意のワード線が起動した時にメモリセルからビット線に送られる非常に小さな信号を検知し、この読み出し(破壊読み出し)によって失われたメモリセルの電圧レベルを元に戻すための書き込みが必要なことです。この技術を発明してから暫くの間、私は、チップの外にあって電圧を検出し増幅するバイポーラ・センスアンプを、スタティックRAMチップで使っていたのと同じように使うものだと考えていました。当時の基本設計則に適した小型アレイであっても、ビット線に割り当てることのできる端末の数には大きな制約がありました。

チップに検出回路を内蔵するのが望ましいことは分かっていましたが、MOS回路で微小電圧を検出する経験は無きに等しい状態でしたし、当時、しきい値電圧(スイッチオンに必要なゲート電圧)の変動はとても大きかったのです。そんなある日、デイル・クリッチロウがやって来て、どこかで聞いてきたという平衡ラッチ回路の話をしました。この回路は、ラッチのアンバランスを生む静電容量の小さな変動を感知するので、タッチ式キーボードに使われていたと記憶しています。この時すでに、同じようなラッチの研究を進めていた研究者もいました。

こちらの図はシュタインらが1972年に発表した論文から引用したものです (Fig. 8)。中央にある検知/リフレッシュ回路は、ラッチの両側にある2本のビット線に接続されたラッチ回路を内蔵しています。両側のビット線は多くのDRAMメ

changes in capacitance which would unbalance the latches. Other people were also working on similar latches at this early time.

This slide (Fig. 8) shows a figure from a paper by Stein et al. published in 1972. The sense/refresh circuit in the center contains a latch circuit connected to two bit lines on opposite sides of the latch. Both bit lines are connected to a large number of DRAM memory cells. Before each memory access, transistors in the sensing circuit balance the voltage on the two latch nodes and the bit lines connected to them to an intermediate voltage level. Then raising the voltage on any word line in this array turns on the transistor in its associated memory cell, causing the capacitor connected to it to charge or discharge a bit line so the latch is unbalanced in a direction corresponding to the voltage stored in the memory cell. The beautiful thing about the latch, when it is activated, is that the small signal unbalance is amplified up to the full digital levels, and those levels are fed right back onto the bit lines where they are written into the memory cells to restore the original levels. This seems to me to be one of the most fortuitously efficient circuits ever devised.

As far as I know, the balanced latch has been used in one form or another in all one-transistor dynamic RAM chips after the first 4-kilobit chips. There have been many improvements and variations.

The defacto standard for many generations of DRAMs is this folded bitline arrangement invented by my esteemed colleague Dr. Kiyoo Itoh at Hitachi in 1974. He took the two bit lines shown on opposite sides of the latch in the previous drawing and folded one over to the opposite side along with its word lines and DRAM cells to form pairs of bit lines being crossed by pairs of word lines, as seen in this slide (Fig. 9). The advantage he discovered is that noises introduced on the pair of bit lines are effectively cancelled out in this arrangement.

Starting in the middle 1970s, our group in IBM Research led by Critchlow worked closely with a manufacturing team in Burlington, Vermont to develop IBM's first one-transistor DRAM chip product shown in the next slide (Fig. 10).

The technology developed for this chip was scaled sufficiently to be able to produce a 64-kilobit chip. The sense amplifiers shown on this slide were based on a new self-compensating design technique invented by my associate Dominick Spampinato and me. I also contributed to a new technique for adding redundant bit lines and word lines which can be used to replace defective lines to greatly improve manufacturing yield. This technique has been widely used for both DRAM and static RAM for many generations since then.

#### Folded Bitline Architecture with 1T1C DRAM Cells

Fig. 9

モリセルに繋がっています。メモリアクセスの前に必ず、検知回路のトランジスタによって、2つのラッチノードとそれに接続されたビット線上の電圧が中間電圧レベルになるようにバランスが取られます。次に、このアレイの任意のワード線上の電圧を上げると、関連メモリセルのトランジスタにスイッチが入り、セルに繋がったコンデンサがビット線の充電あるいは放電を開始し、メモリセルに保持された電圧に対応する方向にラッチはアンバランスになります。ラッチの美しいところは、ラッチが起動することによって微弱な信号のアンバランスがデジタルレベルー杯まで増幅され、その増幅されたレベルがビット線にフィードバックされてメモリセルに書き込まれ、元のレベルが復元されることです。個人的には、この回路はこれまで考案された幾多の回路の中でも、偶然が幸いして結果として効率的なものとなった例の1つではないかと思います。

私が知る限り、このバランスされたラッチは、4キロビット・チップが初めて登場して以来、1トランジスタ型ダイナミックRAMチップには必ず何らかの形で使われています。勿論、その過程で多くの改善がなされ、また、多くのバリエーションが生まれました。

これまでにDRAMは多くの世代を経てきていますが、事実上の標準とされているのは、私が敬愛する研究仲間である日立製作所の伊藤清男博士が1974年に開発したこの折り返しビット線配列です。伊藤博士は、この前のスライドで示したラッチ両側の2本のビット線を取り出し、片側をワード線とDRAMセルと一緒に反対側に折り返し、このスライド(Fig. 9)にあるように、ビット線とワード線を2本ずつ交差さ

# IBM 64 Kbit DRAM Chip

R.DeSimone, et al., 1979 IEEE ISSCC Digest pgs. 154-5

Fig. 10

#### Mid-life crisis: the alpha particle

I was asked to identify difficult challenges in the progression of my work. Just at the time the production 64-kbit chips were being announced, and the dynamic RAM seemed to be getting very mature, the world was becoming aware of two very significant papers. May and Woods of Intel and Yaney, Nelson, and Vanskike of Bell Laboratories revealed that some 16-kbit dynamic RAM's were suffering transient errors due to bombardment by alpha particles. The alpha particles were identified as coming from radioactive impurities in the materials of the hermetically-sealed packages. At first it seemed to have a simple solution — why not modify the package or introduce a barrier layer such as a plastic film between the chip and the package? When experiments like these were done in various labs, the error rates dropped substantially but did not go away, presumably due to radioactive impurities in the on-chip materials. Also, an analysis of the possible soft-error rate due to cosmic rays showed that this source could be significant.

Here was a real crisis! Not only were hordes of people scurrying around to fix up designs of chips then in development or manufacturing, but the whole future of miniaturized MOS integrated circuits seemed to be in jeopardy. Personally, I felt very responsible because of my early role with dynamic RAM's and because I failed to anticipate the problem. Several years earlier I had discussed the possible effect of cosmic rays on dynamic RAM's with an old friend who was knowledgeable about space electronics, but we had concluded that most of the radiation types would pass through with little effect.

せました。この配列によって、2本のビット線に入ってくるノイズを効果的に相殺することができるという利点を博士は発見しました。

1970年代半ばから、IBM研究部門のクリッチロウ率いる私たちのグループはバーモント州バーリントンの製造部門と協力関係を強化し、次のスライドで紹介するIBM初の1トランジスタ型DRAMチップ製品の開発を進めました(Fig. 10)。

このチップのために開発された技術は、64キロビットのチップが余裕をもって作れるようにスケーリングされたものでした。このスライドに示したセンスアンプは、私が同僚のドミニク・スパンピナートと共同で新たに開発した自己補償する設計技術をベースにしています。さらに私は欠陥線の置換を行うことができる冗長ビット線・ワード線を追加するという新しい技術にも貢献し、これにより製造歩留まりの大幅な向上が可能となりました。その後、何世代にもわたってこの技術はDRAMおよびスタティックRAMの両方で幅広く使われています。

#### 「中年の危機」: アルファ粒子

以前、私は研究を進めていく上で難しいと思うことは何か、と聞かれたことがあ ります。ちょうど64キロビット・チップの生産が発表され、ダイナミックRAM技術 もかなり成熟度が高まっていたように思われたその頃、2本の重要な論文が世界の注 目を集めていました。インテルのメイとウッズ、ベル研究所のイエニー、ネルソン、 ヴァンスカイクがそれぞれ、アルファ粒子の衝突によって16キロビットダイナミック RAMに一時的エラーを発生させる場合があるという報告をしたのです。原因とされ たアルファ粒子は、気密封止パッケージの材質に含まれていた放射性不純物が発生源 でした。最初のうちは、例えばパッケージ自体を改良するとか、チップとパッケージ の間にプラスチックのフィルムなどを挿入して障壁層を設けるとかすれば簡単に解決 できると考えられていました。実際に複数の研究所が試したところ、エラー率は大幅 に下がったのですが、ゼロにはなりませんでした。これはチップ上にある物質の放射 性不純物が原因だと考えられました。また、宇宙線が原因だと思われるソフトエラー 率の解析を行ったところ、やはり宇宙線が大きな要因となっていることも分かりました。 これは大問題でした。開発あるいは生産中だったチップの設計の手直しをするため に多数のスタッフが走り回る羽目になっただけでなく、小型MOS集積回路の未来そ のものに黄色信号が灯ったのです。私はダイナミックRAMの黎明期にはそれなりの

Fig. 11

After a long period of doing measurements, developing models, and inventing possible cures, a less threatening view of alpha-particles and cosmic rays emerged. A good quantitative understanding was provided by various modeling techniques which were developed, including a very powerful Monte Carlo approach developed in my team by George Sai-Halasz. It was shown that error rates would rise in response to scaling to smaller dimensions, but that design changes including error-correction techniques would contain the problem. The mid-life crisis was over.

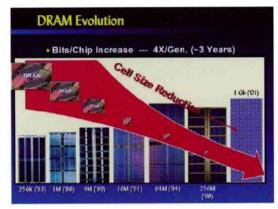

#### Impact of DRAM and Scaling

As the idea of scaling MOS transistors along with all the layout dimensions, interconnect lines, etc. caught on quickly, the microelectronics industry developed a pace for doing this which has given rise to the geometric growth in computer capability since then. Moreover, DRAM became the large-volume, predictable product which drove scaling and silicon chip manufacturing for many years.

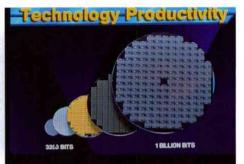

By now I am sure that you understand that DRAM has experienced tremendous productivity increases, which has allowed quadrupling of the number of bits/chip every three years for many generations. This figure (Fig. 11) shows pictures of six generations of IBM chips and shows the reduction in cell size which allowed the increased number of bits. Much of this reduction is due to decreasing all the dimensions of the transistors and wires using the scaling principles. The DRAM cell has been compacted further by making technology improvements which reduce the memory cell area.

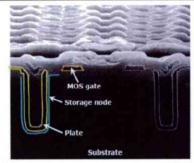

This slide (Fig. 12) shows a big breakthrough started by Dr. Hideo Sunami when

貢献もしてきましたから、こうした問題を予見できなかったということで、個人的に 非常に責任を感じていました。実はその数年前、私は宇宙エレクトロニクスに詳しい 古くからの友人と、宇宙線がダイナミックRAMに与える影響について意見交換する 機会があったのですが、ほとんどの種類の放射線は大した影響を与えることなく通過 するだろう、と結論付けてしまっていました。

その後長い間、計測、新モデルの開発、対処法の発案などが試みられたのですが、そうこうしているうちに今度はアルファ粒子や宇宙線をそれほど警戒する必要はないのでは、という見方も浮上してきました。様々なモデリング技術が開発されたため、定量的な理解を十分に得ることが可能になったのです。私のチームにいたジョージ・サイーハラスが開発した、非常にパワフルなモンテカルロ法もその1つです。そして、スケーリングで寸法を小さくするとエラー率は上がりますが、同時にエラー是正技術などを用いて設計面で対応すれば、こうした問題を抑えられることが示されたのです。「中年の危機」はここに終わりを告げたのです。

### DRAMとスケーリングの影響

すべてのレイアウト寸法や接続配線などと併せてMOSトランジスタのスケーリング(縮小)を行うというアイデアはすぐに受け入れられ、マイクロエレクトロニクス業界はそのペースを上げていきました。これが現在も続く、コンピュータ処理能力の幾何級数的増大の発端です。また、DRAMは大量に生産される予測可能な製品となり、スケーリングやシリコンチップ製造を長い間支えてきました。

DRAMの生産性がこれまで驚異的な伸びを示してきたことは、もうおわかりいただいていると思いますが、チップ当たりのビット数は、何世代にもわたり3年ごとに4倍のペースで増えてきました。この図(Fig. 11)は、IBM製チップの6世代にわたるビット数の増加を可能にしたセルサイズの小型化の歴史を示しています。セルサイズの小型化には、スケーリング則を用いてトランジスタや配線のすべての寸法を小さくしようという取組みが大きく貢献しています。DRAMセルは、メモリセル面積を減らす技術を向上させていくことによって、さらなるコンパクト化を実現してきました。

こちらのスライド(Fig. 12)は、シリコン基板にエッチングしたトレンチ内に3次元コンデンサを形成したDRAMを紹介した角南英夫博士の論文発表に端を発する大きなブレークスルーを示しています。4メガビット・チップ以降のIBM製DRAMに

#### Cross Section of Trench-Capacitor Cells

Fig. 12

# **Cross Section of Stack-Capacitor Cells**

(double fin)

Fig. 13

he published a paper showing DRAM with a three-dimensional capacitor formed in a trench etched in the silicon substrate. Starting with the 4-megabit chip, all the DRAM produced by IBM has used a trench-capacitor technology.

Another three-dimensional capacitor structure called the stacked capacitor is fabricated above the silicon surface rather than below. This technique was pioneered by Dr. Mitsumasa Koyanagi, and has been used widely in the DRAM industry (Fig. 13).

This is a good place to introduce a special picture made at the 2006 annual awards ceremony of IEEE, the worldwide professional society for electronics engineers. The picture (Fig. 14) shows, from the left to the right, Dr. Itoh, Dr. Sunami, me, and Dr. Koyanagi. They were being honored with the Jun-Ichi Nishizawa Medal and I came to celebrate along with them. Notice the fanciful caption "The DRAM father and his three sons in scaling-law". I believe it was supplied by Dr. Sunami. That was a wonderful night. Not long after that, we all wrote articles for a special issue of the IEEE Solid-State

はすべて、このトレンチコンデンサ技術が用いられています。

3次元コンデンサ構造としてはもう1つ、スタックトコンデンサがあります。こちらはシリコンの内部ではなく、表面に形成されます。小柳光正博士が道を開いたこの技術もDRAM業界で広く活用されています(Fig. 13)。

今日はちょうどいい機会だと思いますので、皆様にとっておきの写真(Fig. 14)をお見せしたいと思います。エレクトロニクス技術者の国際的学会であるIEEEの2006年の授賞式での写真ですが、左から伊藤博士、角南博士、私、小柳博士です。この年にお三方が西澤メダルを受賞されるというので、私がお祝いに駆けつけたという次第です。左上に「DRAMの父と『スケーリング則』で結ばれた3人の息子」というしゃれたキャプションが付けられていますが、このフレーズは角南博士がお考えになったのだと思います。とても素晴らしいパーティーでした。それから程なくして、私たちは揃って「IEEE固体素子回路学会」ニュースのDRAM特集号に論文を寄稿しました。

皆様すでにご存じかもしれませんが、DRAMの生産性が向上した理由の1つに、シリコンチップの大型化があります。その際、生産効率を最大化していくためには、これまでより大きな、ウェハーと呼ばれるシリコン基板が必要となります。次のスライドでご説明します(Fig. 15)。

ご覧の通り、シリコン・ウェハーの直径は、開発が始まってから30年間で25ミリから200ミリになりました。

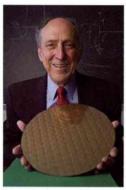

その後もサイズの拡大は続き、新しく建設された大規模工場のほとんどが、この写真(Fig. 16)にあります300ミリのウェハーを採用しています。このウェハーを手にしている私の気持ちを察していただけますでしょうか。非常に軽いものです。現在の300ミリウェハーには4ギガビットのDRAMチップが数百個搭載されています。この写真からもおわかりいただけるように、自分が立ち上げに関わったこの技術を私は大変誇りに思っています。

# チップの大型化によるスケーリング上の課題

チップサイズの大型化や、チップに搭載するトランジスタや回路素子の数の増加 は、「ムーアの法則」として知られる法則に従っています。インテルの創始者の一人 であるゴードン・ムーア氏がこの種の技術の黎明期に予言したことからこの名前がつ

Fig. 14

Fig. 15

Society News which was totally dedicated to DRAM.

You may have noticed that part of the DRAM productivity increase has been due to using larger silicon chips. This has required larger silicon substrates, called wafers, for best manufacturing efficiency as illustrated in the next slide (Fig. 15).

Over the first 30 year period the silicon wafer diameter increased from  $25\ \mathrm{mm}$  to  $200\ \mathrm{mm}$  as shown here.

Since then most of the big new factories have used 300 mm wafers as shown in this photograph (Fig. 16). I hope you realize how it feels for me to hold one of these wafers. It's actually very light. Today's 300 mm wafers contain hundreds of 4-gigabit DRAM chips. As you can see in this picture, I am very proud of what I helped get started.

#### Scaling Challenges due to Bigger Chips

The growth in size of chips and the increasing number of transistors and circuit elements on a chip followed the path known as Moore's Law, which is named after Gordon Moore, one of the Intel founders, who predicted it in the early days. As the complexity of those chips increased, it became very difficult to implement all the numerous wiring interconnections among the transistors, the logic-circuit inputs and the logic-circuit outputs. It became necessary to provide multiple layers of wires. These were organized with all the wires on one layer running perpendicular to the wires on the next level, like streets and avenues in Manhattan in New York City.

As scaling progressed from one generation of chips to the next, the widths of all

いています。チップの複雑度が増すにつれて、トランジスタ、論理回路入力、論理回路出力の間の多くの配線の相互接続をすべて行うことは非常に難しくなり、配線の多層化が必要になりました。この技術というのは、1つの層のすべてのワイヤを次のレベルのワイヤと直角になるように配線する、というもので、例えばニューヨーク市マンハッタンの「ストリート」と「アベニュー」の関係に似ています。

チップの世代移行に伴ってスケーリングが進み、先ほどお話ししたスケーリング則で示唆されていた通り、トランジスタの寸法が小さくなると共に、線幅も細くなりました。そのため、ワイヤの抵抗も個々の線長に合わせて大きくなりました。例えば、大型のチップなどで長い距離を繋がなければならないようなワイヤでは、抵抗値が大変大きくなり、信号伝播速度が非常に遅くなりました。このため、スケーリングは限界に近づいているのではないか、と考えた人が大勢出てきました。私にとっては、対処を要する新たな「危機」でした。

1970年代の後半にスタンフォード大学で何度か講演を行った際、私はこのスライド(Fig. 17)にある階層配線システムを提案しました。シリコン基板上のトランジスタの横に見える、高度にスケーリングされた小さな配線層は、基本ロジック回路のごくローカルな接続にのみ用いられます。それよりも厚く幅も広い金属線のある中央の配線層の抵抗値は、ずっと低くなり、回路の中で離れた位置にあるブロック同士でも接続が可能です。上の層にある非常に大きくて厚いワイヤは、大型のチップ上でも高速度の信号を自在に伝達することによって各種プロセッサの機能やメモリのサブシステムを繋ぎます。また、最上部にある他の厚い配線層はチップにパワーを与えたり、チップ全体にクロック信号を分散してプロセッサ機能をシンクロさせたりすることができます。

スタンフォードを始め、様々な場所で解析やモデリングが行われ、このシステムが 実際に機能することが確認されました。MOS技術でも何世代にもわたって活用され ており、下の方ではさらに集積度を高めたワイヤを用いた層が、上の方ではさらに大 きく、太くなったワイヤを用いた層が徐々に追加されています。また、新しい材料も 次々と採用され、銅線の導入によって抵抗値は下がり、絶縁物の材料の質的向上によ り静電容量も低下しています。

これ(Fig. 18)はIBMが最初に導入した新しい銅線を使ったチップの配線層を高倍率で拡大したものの断面図です。下の方の配線面では小さなワイヤが、上の方では大きなワイヤが使われていることが明確にお分かりいただけると思います。

Fig. 16

#### Interconnect Technology for Microprocessors

- Wire-level hierarchy to reduce RC delay of long wires

- Cu instead of Al to reduce wire resistance

- Low-k insulator instead of silicon dioxide to reduce wire capacitance

- Increasingly limited by surface scattering beyond 65nm generation

Fig. 17

the wires were scaled down along with the transistor dimensions as the scaling principles we discussed earlier suggested. This made the wires much more resistive for a given length of wire. Some of the wires which had to connect longer distances across the bigger chips got very resistive, and the signals propagated very slowly on those wires. Many people thought scaling was nearing an end because of this problem. To me it was another crisis which needed attention.

I remember giving some lectures at Stanford University in the late 1970s, where I proposed the hierarchical wiring system illustrated here (Fig. 17). The highly scaled small wiring layers next to the transistors in the silicon substrate are only used for very local connections of elementary logic circuits. Wiring layers in the middle with thicker and wider metal lines have much lower resistance, so they can be used for long connections between different blocks of circuits. Very large and thick wires in the top layers can carry high-speed signals all the way across the big chips to connect various processor functions and memory subsystems together. Other thick wiring layers at the top can be used to bring in power for the chip and to distribute clock signals across the whole chip to synchronize the processor functions.

A lot of analysis and modeling was done at Stanford and elsewhere to show that such a system can work. It has been in use for many generations of MOS technology, gradually adding more layers with even smaller scaled wires at the bottom and even larger and thicker wires at the top. Also a whole new set of materials were introduced with copper wires for lower resistance and better insulator material for lower capacitance.

This picture (Fig. 18) shows a highly magnified cross section across the wiring

これ(Fig. 19)は下の方の層のワイヤの一部を走査電子顕微鏡で捉えたものです。 ここでは、直角に交差するワイヤがどのように繋がっているのかをお見せするために 絶縁層をエッチング除去しています。現在、最先端の大型プロセッサチップには配線 層が14もあり、数十億の接続点をつなぐ総延長約40 kmの銅線が使われています。こ のように、集積回路が正常に動作するためには、ワイヤもトランジスタに負けず劣ら ず重要な役割を果たしているのです。

# DRAMとスケーリング・アプローチの成熟

1979年にIBMのフェローになってから、私はDRAMとスケーリングの更なる進化、ある意味でのスケーリング則の一般化、そして1972年の時点ですでに予見できていた、いくつかのスケーリングの限界に対応する方法を見出すことに主に時間を割いてきました。その限界というのは例えば、より良い導電性材料の必要性が高まってきたことや、電圧が1ボルトを大きく下回った時にトランジスタのスイッチがきれいにオン/オフしないことなどです。こうした問題がネックとなって、プロセッサのスピードは過去10年間、踊り場にあります。一方、トランジスタやワイヤの寸法の更なるスケールダウンを可能にする構造改良の研究は続けられています。現在の主な目標は、さらにエネルギー効率を上げ、数千個から数百万個のプロセッサを抱える大規模データセンターにおいて、一定のエネルギー量でより多くの計算を行えるようにすることです。この問題、ならびにその解決に向けて私が最善であると考えている技術的な方策については、明日のワークショップでお話ししたいと思います。

この業界で活躍する数多くの人々による幾多のプロセス改良、構造に関わる革新、そして何よりその愚直な努力のおかげで、集積回路のあらゆる寸法は40年間で約150分の1にまで縮小し、今後も更なる小型化が期待できることを私は大変誇りに思っています。その結果とも言うべき、コンピュータが私たちの生活にもたらした進化と変化は掛け値なしに素晴らしいものです。ところで、皆さんは私が初めてメモリチップを設計した時、計算尺を使っていたということを想像できるでしょうか。なぜこのような話をするかというと、皆様に「40年後の世界はどのようになっているだろうか」と考えていただきたいからです。今日も自分のキャリア形成を始めたばかりの若い方がたくさんいらっしゃっていますが、そうしたことを考えることは、皆さんにとってチャレンジであると同時に、チャンスでもあるのです。皆さんの目の前にも今

Fig. 18

# CMOS/Cu Technology METAL 2 VIA METAL 2

Fig. 19

layers in a chip with the new copper wires first introduced by IBM. You can clearly see the smaller wires in the lower wiring planes and the larger wires in the top planes.

Here (Fig. 19) is a scanning-electron microscope picture of some of the lower-level wires with the insulating layers etched away to show how wires in one direction are connected to wires in the perpendicular direction. Today's latest large processor chips have as many as 14 wiring layers, and the billions of interconnections use a total of about 40 kilometers of copper wire. The wires are truly as important as the transistors in making integrated circuits work.

#### **DRAM** and Scaling Approach Maturity

Since I became an IBM Fellow in 1979, my career after that has been spent on helping DRAM and scaling continue to advance, generalizing the scaling rules in certain respects, and finding ways to live with some of the scaling limitations we were already able to predict in 1972. These limitations include the increased need for materials with better conductivity, and the inability to scale the voltage much below one volt and still have the transistors switch on and off cleanly. These problems have caused a leveling off in processor speeds over the last ten years. Work has continued to bring in improved structures to allow further scaling down of transistor and wire dimensions. The main goal now is to improve energy efficiency to allow large data centers with thousands to millions of processors to provide more computing for a given amount of energy. I plan to discuss this issue, and what I see as the best technical path toward solving it, in my talk at tomorrow's workshop.

とは全く違った世界を作っていくチャンスが広がっているのです。

#### 創造性と未来へのチャレンジについて

前千年紀における科学技術の目覚ましい発展と前世紀におけるその急激な加速は、 人類の驚くべき創造性が可能にしたものです。しかし、そもそも「創造性」とは一体 何なのか、誰がそれを持っているのか、どうすればそれを刺激することができるのか などについてはほとんど知られていません。実際、「創造性」についての知識や理解 があまり進んでいませんから、「創造性」を用いて少しでも何かを成し遂げたことの ある私のような人間であれば「創造性」について少しは興味深くて役に立つ話ができ るのではないかと思いました。ですから、今日はいつもの謙虚さは少し横に置いて おき、あえて「創造性」に関する私個人の考えや経験についてお話ししたいと思いま す。何より「創造性溢れる」人というのは、チャレンジせずにはいられない性質です から。

では改めて伺います。「創造性」とは一体何でしょうか。それは一部の人間が持つ 知的能力であり、脳の中に眠るものであり、コンピュータをもってしても未だ追いつ けないものです。私の理解では、それはそれまで存在しなかった新しい何かを生み出 し、存在せしめる力で、私たちの知識の基盤の延長線上にあるものです。生業として 研究を行っている者にとって、「創造性」とは自分の仕事を極めるために必要な特性 であるとも言えます。これまでの私の経験は、そのほとんどが科学あるいは工学的知 識と能力の延長線上にありますが、私の持つ視点は芸術の分野にも応用できる部分が あるのではないかと思います。

私の経験では、「創造性」とは、新しい、未知の世界への「突然の」飛躍を可能とするものです。夜中に突然目が覚めると、それまで取り組んでいた問題の解決方法が頭の中にできていた、といったことはしばしばありました。寝ている途中でベッドから起き出してメモや絵を残し、またそのまま眠りにつくなど、数多くの発明家がこれに似た経験について語っています。また、車を運転中に重要な発明をしたと言う人もいます。少なくとも携帯電話が普及するまでは、心に十分な余裕があったからでしょう。私がDRAMのメモリセル構造を発明したのは、先ほどお話しした通り、ライバルチームがその研究プロジェグトについて発表するのを聞き、刺激を受け、触発されて帰宅した、ある夕方のことでした。基本的なアイデアは一瞬で思いついたのです

I am very proud to say that with many process improvements, structural innovations, and plain hard work, the thousands of people who make up this industry have been able to achieve in forty years a reduction in all dimensions of integrated circuits by a factor of about one hundred fifty, and more is still expected. The results of that, the ways that computers have advanced and changed our lives have been truly amazing. Can you imagine that I used a slide rule to design my first memory chip? The point of bringing that up is to ask the question, what will the world be like in another forty years? This is the challenge and the opportunity for the young people in the audience here today who are just starting their careers. You also have a chance to create a greatly different world in your time.

#### On Creativity and Challenges for the Future

The tremendous progress in science and technology in the last millennium and its rapid acceleration in the last century is due to the remarkable creativity of mankind. Yet so little is known about creativity — what is it, who has it, how can it be stimulated? Apparently so little is known and understood about this subject that it is assumed a person like me, with some demonstrated record of accomplishment in creativity, can say something interesting and useful about it. So I have decided to suspend my normal humility and accept the challenge to write about my own personal thoughts and experiences in this area. Above all, creative people cannot resist a challenge.

So, what is creativity? It is an intellectual capability of some human beings, something that goes on in the brain, something not yet matched by computers.

According to my understanding, it is the ability to produce or bring into existence something that was not there before, something new, an extension of our base of knowledge. In other words, for those of who have undertaken research as a career, it is a necessary trait to excel in our jobs. Most of my experience has been with the extension of scientific or engineering knowledge and capability, but I suppose some of my observations may apply to artistic fields as well.

My experience with creativity is that it can produce a sudden leap into the new and previously unknown. I often wake up in the middle of the night with a solution to a problem which I have been working on previously. Many inventors have described similar experiences to me, including getting out of bed to make notes or drawings before going back to sleep. Others have described significant inventions made while driving, which apparently leaves a lot of the mind free, at least before cell phones. As I

が、もう一度閃きを得て、最終的にトランジスタを1つにするという単純化にたど り着いて、それが完成に至るまでには2ヶ月ほど時間を要しました。

では誰がそういった「創造性」を持っているのでしょうか。長い間、似たような環境に置かれた研究仲間が歩んできたキャリアを目撃してきた経験から言うと、人には創造性を持った人とそうでない人がいます。創造性がない人でも、創造性のある人と同等、あるいはそれ以上の優れた分析力を持っていたり、理路整然と物事が処理できたり、発信力が高かったり、全体として信頼に足る、有用な人物だったりすることがあります。しかし、研究所では創造的アウトプットを基準として評価されるため、研究者の採用にあたっては志望者の「創造性」の見極めが鍵となります。私は、創造的な考え方とは、基本的に、重要な問いかけを行い、優れた解を見出すプロセスであると思います。そのため、私は面接においては、的を射た鋭い質問をする人物に高い評価を与えると共に、基本的な事項を利用して答えを出す能力があるかどうかを見るようにしています。

調査表を用いて「創造的な」人物の輪郭を明らかにしようとする試みがあることは 承知していますが、それがどれ程の成功を収めているかは寡聞にして存じません。近 年、私は幸運にも、重要かつ創造性溢れる功績に対して顕彰を受けるような人々の末 席に加えていただいているのですが、そうした人々を見ていて思うのは、彼らは確か に興味深い人物だが、見たところは普通の人である、ということです。以前、米国 発明家殿堂のあるイベントで、殿堂入りを果たされた4人の発明家の方々と話をさ せていただく機会があったのですが、私を含めた5人全員が地方や田舎町の出身で、 ほとんど皆、教室が1つしかない学校で初等教育を受けていた、と知りました。私 たちは、一人で放っておかれたことが多く、たっぷり与えられた自分の時間を使って 人生についての考えを深めていったのです。そうした経験がその後の成功の鍵となっ たとは断言できませんが、少なくとも今の若い世代の人々に必要であると考えられて いることの多くとは相容れないものでしょう。また、私がじっくりとものを考えるこ とを身につけたのも小さい時でしたが、そうした習慣のおかげで、問題解決に集中で き、頭脳のすべてを使って創造的な解決策を考えることができるようになったのでは ないかと思います。 described previously, my invention of the DRAM memory cell came early one evening after I came home stimulated and challenged from listening to a talk about a competing research project. The basic idea came in a moment, but there were a couple of months of perfecting it before the final simplification to a single transistor came in another flash of inspiration.

Who has creativity? 1 know from experience in following careers of associates in similar environments over long periods of time that some are creative and others are not. The ones who are not creative can be equal or superior in analytical capability, well organized, good communicators, and, overall, very solid and useful individuals. But research institutions are measured on their creative output, so it would be good to be able to identify creativity in employment candidates. I believe that creative thinking is basically a process of posing significant questions and finding good answers. So I give a lot of credit in interviews to those who ask relevant, penetrating questions, and I also try to examine their ability to apply fundamentals to answer questions.

I know that there have been attempts to develop profiles of creative people using questionnaires, but I don't know how successful these have been. I have been fortunate in recent years to be included in groups of people who have received major honors for significant creative achievements, and I find them very interesting but apparently ordinary people. At a National Inventors Hall of Fame event, while I was talking with four other inductees, I discovered that all five of us were raised in rural areas or small towns, and most started their education in one-room schoolhouses. We all were left on our own a lot with plenty of free time to develop our ideas about life. Now that may not be the key to our subsequent successes, but it surely is a counter argument to many of the things which are considered necessary for the younger generation today. I developed a very slow thinking process in my early days, and I believe that is why I am able to bring great concentration to a problem and engage my whole brain in finding a creative solution.

#### How can creativity be nurtured and stimulated?

I have a motto posted in my bedroom where I see it every morning which reads, "ATTITUDE IS EVERYTHING." It was given to me by my ballroom dance teacher, but it applies to many other pursuits. I believe it is the key to unleashing creativity. A great many have the intelligence, many have the preparation, some are at the right place at the right time, and only a few realize that they have the mission and ability to make a

# どうすれば「創造性」を育て、刺激できるのか

私は寝室に自分のモットーを掲げ、毎朝見るようにしています。それは、「姿勢こそがすべて」というものです。この言葉は社交ダンスの先生にいただいたものですが、ダンス以外にも当てはまります。私はこの言葉こそが「創造性」を引き出す鍵ではないかと思います。知性を備えた人は非常に多いですし、準備が出来ている人もたくさんいますし、しかるべき時にしかるべき場所にいる人もいます。しかし、自分には世界を大きく変える能力と使命があると自覚している人はごく僅かしかいません。私の場合、この「姿勢」は、これまでの人生の節目節目で、与えられた最高のチャンスを活かすべきだと励まし、私に大きな影響を与えてくださった人々のおかげで獲得したものと考えています。また、博士課程での指導教官は、私が自分の研究分野で世界をリードする存在になることを期待されているのだということに気付かせてくれました。

1950年代後半、IBMに入社した時には、コンピュータ技術を発展させるという明確な使命がありました。特許が取れそうなアイデアを記録するため、技術者にはノートが配られ、「発明」を促されました。今思えば、その頃のプロジェクトはいささか強引すぎましたが、私たちは情熱を持って研究に勤しんでいました。先ほどもお話ししましたように、1960年代の半ば、私を含め何人かの研究者が選抜され、当時生まれたばかりのMOS技術の活用を目指し、それほど大きくないプロジェクトで技術開発を行うことになりました。難しい技術ではありましたが、課題さえ潰していけば大きな可能性がありました。私は、上司から、この技術を使ってメモリを作る最善の方法を見つけるようにと言われました。私はすでに準備ができており、姿勢も申し分ありませんでした。一歩前に進む毎に自分の姿勢を確認し、自らを鼓舞しました。私はまさにしかるべき時にしかるべきプロジェクトに携わっており、何より自らの使命を自覚していました。

今日、時代は変わり、技術面での好機は別のところにあります。しかし、「創造性」を育み、それが開花する環境を整えるためには、今もなおモチベーションとリーダーシップこそが欠かせないと私は信じて止みません。

major difference in our world. I believe my "attitude" was developed with the aid of some influential people at each step who urged me to pursue the best opportunity which was available. At the Ph.D. level my thesis advisor made me aware that I was expected to become the worlds' expert in the subject of my research.

When I joined IBM in the late 50s there was a clear mission to advance the computer art. We were issued engineering notebooks to record our patentable ideas and told to invent. Our early projects, in hindsight, were a little farfetched but we pursued them with enthusiasm. In the mid 60s as I told you before, some of us were assigned to do the engineering for a modest sized program trying to exploit the very new MOS technology. It was a tough technology, but it had great potential if we could solve the problems. My manager told me to find the best way to do memory with this technology. I was ready. I had a very good attitude. I had been groomed and motivated at every step. I was working on the right project at the right time, and I knew my mission.

Today times have changed, and the technical opportunities are in different areas. I believe that motivation and leadership remain essential to nurture creativity and provide an environment where it can flourish.

#### Is there still a need for creativity?

Yes, of course, in a general sense the need for creativity in the future is obvious. On the other hand, if we look in some detail at where the world appears to be headed, we can readily see that the need is indeed critical. The rapid pace of industrialization of the previously underdeveloped nations and the projected growth of populations is leading us to a time where there will be severe impact on the resources and environment of our finite globe. Surely future generations must be preoccupied with understanding and mitigating those effects.

Major advances are clearly needed in energy supply and distribution. We must face a crisis of both limited supply of energy resources and major environmental deterioration due to using it. The field of transportation, which has seen such major advances in the recent past, is clearly not on a course which is scaleable to the future needs of society due to its high energy demands. Also, the really big problems of the past remain; future generations must still face disease, hostile fellow humans, and natural disasters of a tumultuous earth and a chaotic universe. These challenges present a broad range of opportunity for creative solutions, where meaningful goals can range from complete cures to merely improving chances of survival.

#### 現在も「創造性」は必要か

勿論、一般的な意味で今後も「創造性」が必要であることは明らかです。また、現在、世界が進もうとしている方向を注意深く見てみると、やはり「創造性」は必要不可欠であることが容易に分かります。これまで発展途上とされてきた国々においても急速に工業化が進み、世界の人口がますます増大すると予測される中、今後更に、地球環境や限りある資源に深刻な影響が表れてくることでしょう。必ずや、これからの世代の人々はそうした現象を理解し、その影響を軽減することに忙殺されることになるはずです。

エネルギーの供給や分配といった問題に大きな進展が必要なのは火を見るよりも明らかです。私たちは限られたエネルギー資源の供給やエネルギーを消費することによる大規模な環境の悪化という危機的状況に対峙していかなければならないのです。近年大きな発展を遂げてきた輸送分野は大量のエネルギーを必要とするものですが、これからの社会のニーズに合わせてその規模を調整するという方向には進んでいないことは明らかです。また、過去から存在し続ける、途方もなく大きないくつかの問題も未解決のままです。すなわち、これまでの世代がそうだったように、これからの世代も病気と闘い、敵意のある人間と向き合い、何かと騒がしい地球や混沌とした宇宙で起こる天災と折り合いをつけていかなくてはなりません。しかし、こうしたチャレンジは創造的な解決方法を生み出す多様なチャンスであり、完璧な治癒から単なる生存率の向上に至るまで、意義深いゴールは多岐にわたります。

この半世紀ほどで通信技術やコンピュータの能力は大きな進歩を遂げました。情報 技術や、情報を生み、発信し、提供する手段において、これからも「創造性」は必要 とされるのでしょうか。私の答えは「イエス」です。こうしたツールは経済的生産性 の維持向上に欠かせないものとなっており、先に挙げた重要な問題を解決していく過程においても大切な役割を果たすからです。

# 「創造性」が導く未来とは

科学技術が今後どのようなペースで進歩していくかを示したグラフはいずれも、株価のチャート同様、どこまでも前進することを示しています。しかし、過去のすべての世代がそうであったように、私たちはやり方を知っていることについてはすべてを

Are there needs for further creativity in information technology, the means for generating, distributing and presenting information, after the major advances in communication and computing capability in the last half century? Yes, because these tools have become indispensable to economic productivity, and can play a major role in the solutions to the important problems which I described.

#### Where will creativity lead in the future?

Every trend curve says that the pace in science and technology, like the stock market, will move ever onward. But we, like every preceding generation, have done everything we know how to do and are unable to see much beyond the next steps which are already in place. We must also consider the possibility that our last century's prodigious progress has seriously depleted the pool of unknown knowledge left for future scientists to bring forth. Certainly, it appears that there are a limited number of laws of physics and chemistry governing our universe and a limited number of basic elements. We may be close to completing our understanding of the essential implications and properties of all of these. Therefore, the future may not hold surprises so fundamental as the radio and the transistor.

However, the advances of the future in the physical sciences will likely still be astonishing in their impact on society. Hopefully this will include some breakthroughs that allow nuclear power to be fully harnessed. Also, computers will likely be devised with so much creative capability that the question of whether they think will become irrelevant. The biological sciences appear to be breaking forth into their golden age. The questions there are not how far they can go, but how far should they go.

In summary, whether or not we understand exactly how human creativity comes about, its impact on the world we live in is profound. I am optimistic that our creativity will give us the knowledge and tools to clean up the major messes and avoid the potential disasters that our technology advances have spawned. Clearly more than science and technology will be needed in this respect. Hopefully, the global infrastructure which science and technology have provided will help solve the critical global problems facing future generations.

In closing I want to thank the Inamori Foundation once again for this great honor.

やり尽くしてしまい、次の手を打ったのはいいものの、その先があまり見えないという状態です。また、前世紀にとてつもない進歩を果たしてしまったがために、これからの科学者たちには解明すべき未知の知識がほとんど残されていないのではないか、ということについても考えなくてはなりません。言うまでもなく、この宇宙を支配している物理や化学の法則、あるいは基本的な要素には数に限りがあると思われます。私たち人類はこうしたものすべてが持つ重要な意味合いや性質を理解していくというプロセスの終わりに近づいているのかもしれません。したがって、これからの未来にはラジオやトランジスタのように、私たちに基本的なことで驚きを与えてくれるものは残されていないかもしれません。

にもかかわらず、物理科学がこれから成し遂げる進歩は、これまでと同様、計り知れない影響を社会に与え続けることでしょう。そうした新たなブレークスルーに、原子力を完璧にコントロールする技術が含まれることを願いたいものです。また、コンピュータはその開発にこれからも非常に多くの創造力が活用されるでしょうから、「コンピュータは考えることができるのか」といった問いは意味を持たなくなるでしょう。一方、生物学は一気に黄金時代へと突入しているようで、「どこまで行けるのか」ではなく「どこまで行くべきか」が問題となっています。

まとめますと、人間の「創造性」の源が何であるのかについての正確な理解の有無にかかわらず、私たちが住む世界に及ぼすその影響力は絶大です。私は楽観的な考え方の持ち主で、「創造性」が与えてくれる知識やツールは、現在の混沌とした状況を一掃し、技術の進歩の弊害としてもたらされる不幸な出来事を回避してくれるものと考えています。言うまでもなく、こうしたことを実現するには科学技術だけでは不十分です。科学技術がこれまで提供してきた世界的なインフラが、未来の世代が直面するであろう重大な地球規模の危機の解決に役立つことを願うばかりです。

最後になりましたが、このような栄誉を授けてくださった稲盛財団の皆様に再度御 礼を申し上げます。

# 稲盛財団2013---第29回京都賞と助成金

発 行 2014年8月20日

制 作 公益財団法人 稲盛財団

〒600-8411 京都市下京区烏丸通四条下ル水銀屋町620番地

Phone: 075-353-7272 Fax: 075-353-7270

E-mail admin@inamori-f.or.jp URL http://www.inamori-f.or.jp/

ISBN978-4-900663-29-9 CO000